# Simulation Control of Platforms and Modules User Guide

# Imperas Software Limited

Imperas Buildings, North Weston, Thame, Oxfordshire, OX9 2HA, UK docs@imperas.com

| Author:     |                                                            |

|-------------|------------------------------------------------------------|

| Version:    | 2.5                                                        |

| Filename:   | Simulation_Control_of_Platforms_and_Modules_User_Guide.doc |

| Project:    | Simulation Control of Platforms and Modules User Guide     |

| Last Saved: | October 11, 2021                                           |

| Keywords:   | Module Platform API                                        |

# **Copyright Notice**

Copyright © 2021 Imperas Software Limited All rights reserved. This software and documentation contain information that is the property of Imperas Software Limited. The software and documentation are furnished under a license agreement and may be used or copied only in accordance with the terms of the license agreement. No part of the software and documentation may be reproduced, transmitted, or translated, in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without prior written permission of Imperas Software Limited, or as expressly provided by the license agreement.

## Right to Copy Documentation

The license agreement with Imperas permits licensee to make copies of the documentation for its internal use only. Each copy shall include all copyrights, trademarks, service marks, and proprietary rights notices, if any.

#### **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

#### Disclaimer

IMPERAS SOFTWARE LIMITED., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

# Table of Contents

| 1   | Preface                                                                      | 7            |

|-----|------------------------------------------------------------------------------|--------------|

|     | 1.1 Notation                                                                 | 7            |

|     | 1.2 Related Documentation                                                    | 7            |

|     | 1.3 Glossary / Terminology                                                   | 7            |

| 2   | Introduction                                                                 |              |

|     | 2.1 Prerequisites                                                            | 9            |

|     | 2.2 Obtaining & installing the OP API                                        |              |

|     | 2.3 Compiling Examples described in this Document                            |              |

|     | 2.4 Shared Objects and executables                                           |              |

|     | 2.5 Platforms, Modules and Shared Objects                                    |              |

| 3   | Simulating Modules using harness.exe                                         |              |

| 4   | Imperas Simulation Overview                                                  |              |

| -   | 4.1 Simulation Environments.                                                 |              |

|     | 4.2 What are OVPsim and CpuManager?                                          |              |

|     | 4.3 Use of OP with Imperas tools                                             |              |

|     | 4.4 C API and iGen                                                           |              |

| 5   | Separation of iGen modules and C harness / testbench                         |              |

| 6   | Documentation on the OP API                                                  |              |

| 7   | Introducing a C harness / testbench                                          |              |

| ,   | 7.1 Writing a harness using C++                                              |              |

|     | 7.2 Naming of classes and methods                                            |              |

|     | 7.3 Example                                                                  |              |

| 8   | The top level or root module                                                 |              |

| 9   | Configuring the Simulation using parameters                                  |              |

|     | 9.1 Parameter Lists on a Root Module                                         |              |

|     | 9.1.1 The available root module parameters                                   |              |

|     | 9.2 Using Overrides to Set parameter values on module and component instance |              |

|     | 9.3 Configuring Modules and Components from Harness                          |              |

|     | 9.3.1 Module Hardware Parameters                                             |              |

|     | 9.3.2 Component Feature Parameters                                           |              |

|     | 9.3.3 Setting Parameters in the Harness                                      |              |

|     | 9.3.3.1 Parameter List                                                       |              |

|     | 9.3.3.2 OP PARAMS Macro                                                      | . 27<br>. 28 |

|     | 9.3.4 Running Example                                                        |              |

|     | 9.4 Special parameter values                                                 |              |

|     | 9.4.1 MIPS parameter                                                         |              |

|     | 9.4.2 Endian parameter                                                       |              |

|     | 1                                                                            |              |

| 1.0 | 7 · · · · · · · · · · · · · · · · · · ·                                      |              |

| 10  | Controlling the simulation using the Command Line                            |              |

|     |                                                                              |              |

|     | 10.2 Verbose Output                                                          | . 54<br>24   |

|     |                                                                              |              |

|     | 10.3 Passing arguments into application programs                             | . 33         |

| 10.4 Use of debugging options                                          | 36      |

|------------------------------------------------------------------------|---------|

| 10.5 Adding harness specific command line options                      |         |

| 10.5.1 Argument Conflicts                                              | 39      |

| 10.6 Other useful command line options                                 | 39      |

| Writing your own harness.exe                                           | 42      |

| Monitoring / Tracing during simulation                                 | 47      |

| 12.1 Processor Model Tracing Operations                                |         |

| 12.1.1 Tracing control on the command line                             | 47      |

| 12.1.2 Tracing control with CPU model parameters                       | 48      |

| 12.1.3 Tracing control with OP functions                               |         |

| 12.2 Processor Instruction Tracing Example                             |         |

| 12.3 Peripheral model parameters                                       | 51      |

| 12.3.1 Obtaining parameter lists (usingshowoverrides)                  | 51      |

| 12.3.2 Configuration                                                   |         |

| 12.3.3 Diagnostics                                                     | 54      |

| 12.3.3.1 On a single Instance                                          | 54      |

| 12.3.3.2 On all instances in a design                                  | 55      |

| 12.4 Adding your own monitors in a harness                             | 55      |

| 12.4.1 Monitoring nets with callbacks                                  | 56      |

| 12.4.1.1 Finding nets and declaring net callbacks                      | 56      |

| 12.4.1.2 Simulating with net callbacks                                 | 57      |

| 12.4.1.3 monitoringNets/harness/harness.c full listing                 | 58      |

| 12.4.2 Monitoring Bus / Memory / Processor Address accesses using Call | backs59 |

| 12.4.2.1 Find buses and memories and attach callbacks                  |         |

| 12.4.2.2 Running the example                                           |         |

| 12.4.3 Adding a command to show module contents                        | 61      |

| 12.5 Writing a Monitor module                                          | 62      |

| 13 Simulating Processor Exceptions                                     | 63      |

| 13.1 Example of Simulating an Unaligned Access Exception               |         |

| 13.2 Enabling simulation of exceptions with overrides on command line  |         |

| 13.3 Enabling simulation of exceptions in modules                      |         |

| 13.4 Enabling simulation of exceptions in a C harness                  |         |

| 14 Semihosting and Intercept Libraries                                 | 66      |

| 14.1 Selecting semihost libraries                                      |         |

| 14.1.1 Specifying a semihost library in the module.op.tcl              |         |

| 14.1.2 An assembler test program                                       |         |

| 14.1.3 Adding imperasExit semihost library to harness.c                |         |

| 15 Imperas built-in Application Intercepts                             |         |

| 16 Simulator Control Files                                             |         |

| 16.1 Specify use of Control File on the simulator command line         |         |

| 16.2 Specify use of Control File using IMPERAS_TOOLS                   |         |

| 16.3 Specify use of Control File in a C harness                        |         |

| 17 Loading an Application Program file                                 |         |

| 17.1 Load Address Support                                              |         |

| 17.1.1 LMA vs VMA                                                      |         |

| 17.1.2 Load Physical                                                   | 73      |

| 17.2 Program Load Options                                     | 73 |

|---------------------------------------------------------------|----|

| 17.2.1 Set Start Address                                      | 73 |

| 17.2.2 Zero BSS Section                                       | 73 |

| 17.3 Loading a Program onto Processors using the Command Line | 74 |

| 17.3.1 Loading onto single or multiple processors             |    |

| 17.3.2 Modification to Load Address                           |    |

| 17.3.3 Specifying the start Address                           | 75 |

| 17.3.4 Provide Arguments to Applications                      | 76 |

| 17.4 Common Program Memory                                    |    |

| 17.5 Loading an application from the harness                  | 77 |

| 17.5.1 Application Loader Controls                            |    |

| 17.5.2 Onto a Processor Instance                              | 77 |

| 17.5.3 Onto a Bus Instance                                    | 77 |

| 17.5.4 Onto a Memory Instance                                 | 78 |

| 17.6 Getting Information of Loaded Applications               | 78 |

| 17.7 Example                                                  | 78 |

| 17.8 Loading Program Symbolic information                     | 81 |

| 17.8.1 Command Line                                           | 81 |

| 17.8.2 In a Harness                                           | 81 |

| 17.9 Defining a hardware resident program                     | 81 |

| 17.10 Custom Application Loaders                              | 82 |

| 17.10.1 Writing a custom reader                               | 82 |

| 17.11 Custom Loader using Standard Object Reader              | 82 |

| 18 Attaching a debugger                                       |    |

| 18.1 Introduction                                             |    |

| 18.2 Debug with GDB                                           |    |

| 18.2.1 Starting GDB debug session on a single processor       |    |

| 18.2.1.1 Command line                                         |    |

| 18.2.1.2 Root module instance                                 |    |

| 18.2.2 Selecting Processor(s) to debug with GDB               |    |

| 18.2.2.1 Using command line options                           |    |

| 18.2.2.2 In a C harness                                       |    |

| 18.2.3 Configuring GDB                                        |    |

| 18.2.4 Using GDB with eGui Graphical User Interface           |    |

| 18.3 Debug with MPD                                           |    |

| 18.3.1 Configure MPD                                          |    |

| 18.3.1.1 Debug Peripheral model constructors                  |    |

| 18.3.1.2 Add to source search path                            |    |

| 18.3.2 Using MPD with eGUI                                    |    |

| 18.3.3 MPD Batch Mode                                         |    |

| 18.4 Manual Debug connection specifying port                  |    |

| 18.4.1 Do not wait for debug connection                       |    |

| 18.5 Using Control Files                                      |    |

| 18.6 Example of Debugging Applications                        |    |

| 18.6.1 Debug all processors                                   |    |

| 18.6.1.1 Using gdbconsole                                     | 91 |

## Simulation Control of Platforms and Modules User Guide

|      | 18.6.1.2 Using MPD with the Imperas Professional Simulator    | 92  |

|------|---------------------------------------------------------------|-----|

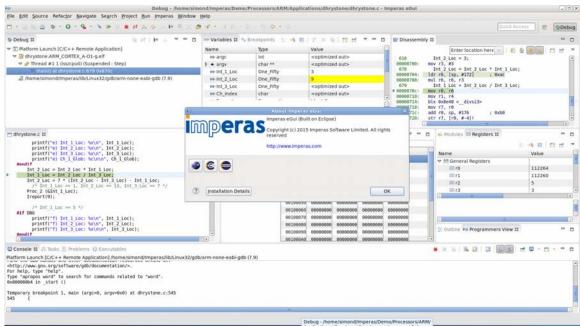

| 19   | Imperas eGui Graphical Debug Environment                      | 95  |

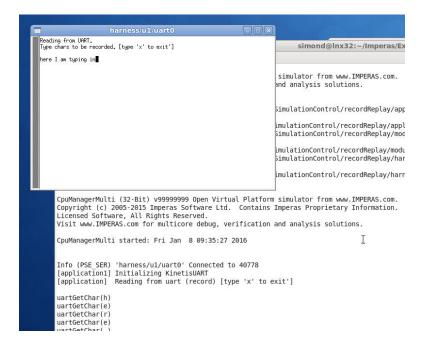

| 20   | Controlling Record and Replay of Virtualized Peripheral Input | 96  |

| 20.1 | 1 Example for Record Replay operation                         | 96  |

| 20.2 | 2 Simple CPU Memory and UART module                           | 96  |

| 20.3 | 3 Application                                                 | 97  |

| 20.4 |                                                               |     |

| 20.5 | 5 Using instance parameters                                   | 99  |

| 20.6 | •                                                             |     |

| 21   | OP API Compatibility with deprecated ICM API                  | 101 |

| 21.1 | 1 Interoperability                                            | 101 |

| 21.2 | 2 API tracing                                                 |     |

| 22   | ICM to OP API Function Conversion                             |     |

### 1 Preface

The Imperas simulators can use models described in C or C++ and the models can be exported to be used in simulators and platforms using C, C++, SystemC or SystemC TLM2.

This document describes how the simulator is controlled, how virtual platforms are loaded and simulated, how testbenches and harnesses are written.

This document specifically describes how the OVP OP C API is used in C programs for use with Imperas and OVP virtual platform simulators and tools.

#### 1.1 Notation

Code Text representing code, a command or output from *iGen*.

*keyword* A word with special meaning.

#### 1.2 Related Documentation

There are several documents available as PDF:

Getting Started

• Imperas Installation and Getting Started Guide

Interface, API, and iGen related

- OVP Peripheral Modeling Guide

- OVPsim Using OVP Models in SystemC TLM2.0 Platforms

- iGen Model Generator Introduction

- iGen Platform and Module Creation User Guide

- Imperas Peripheral Generator Guide (using iGen)

Usage of Modules and Peripherals created using iGen

- Simulation Control of Platforms and Modules User Guide

- Advanced Simulation Control of Platforms and Modules User Guide

# 1.3 Glossary / Terminology

**OP API** - OVP Platforms API - C API used for creating and controlling virtual platforms. 2nd generation API, replaces ICM API. iGen creates modules/platforms in C using this API.

**iGen** - Imperas productivity tool that has a powerful script-based function API that is used to create C/C++/SystemC models and templates. Described in the iGen Model Generator Introduction, and for platforms, in the iGen Platform and Module Generator User Guide.

**OVPsim** - Simulator for Open Virtual Platforms that executes platforms and models coded in the OVP APIs

**CpuManager** - Imperas commercial simulator that fully implements the APIs defined by OVP (OVPsim implements a subset)

**Platform** / **Module** – a collection of components connected together into a level of hierarchy in a system to be simulated. This is a program in C/C++ making calls into OP API and normally compiled into a shared object/dynamically linked library and loaded by the simulator at run time.

**Testbench / Harness** – (used interchangeably) – A program in C/C++ making calls into the OP API to connect and control OVP components. It is normally linked to the simulator to provide an .exe binary that can be executed. Used to instance one or more platforms/modules and controls their execution. The main difference, from a platform/module, is that a testbench or harness includes a definition of the function main(), may include a command line parser and is linked to create an executable binary (.exe) file.

**Root Module** - used to describe the initial platform/module that instances one or more platforms/modules and controls their execution. Used in the testbench / harness.

## 2 Introduction

Imperas simulation technology enables very high-performance simulation, debug and analysis of platforms containing multiple processors and peripheral models. The technology is designed to be extensible: you can create your own platforms, new models of processors, and other platform components using interfaces and libraries supplied by Imperas. Platform models developed using this technology can be used both with Imperas simulation products and the freely-available OVPsim platform simulator.

Simulations are controlled by using the provided harness.exe program, or for more sophisticated control, and bespoke harness or testbench is written in C/C++ using the OVP OP API.

This document explains the usage of the OP API to write harnesses / testbenches. It explains the structure of modules and the different simulator phases, and how they are controlled.

## 2.1 Prerequisites

Since harnesses and testbenches for use with Imperas and OVP tools are written in C, an important prerequisite is that you must be proficient in the C language. If you want to use C++ then it is expected that you are proficient in the use of C++ and how it uses a C API.

# 2.2 Obtaining & installing the OP API

The OP API is part of all Imperas / OVP installations and thus you should already have it installed and be ready for use.

# 2.3 Compiling Examples described in this Document

The examples use modules, processors, component models and tool chains, available to download from the www.OVPworld.org website or as part of an Imperas installation.

The compilation of the examples utilizes the use of a Makefile, the instructions for which indicate the use of the command *make*, on Windows systems the MinGW *mingw32-make* command should be used in its place.

The Makefiles referred to in this document are written for GNU make. Standard Makefiles supplied by Imperas support compilation and linking using GNU tools on both Windows and Linux.

Example scripts will be referred to as (for example) *example.sh*, this being the extension used on Linux or for Windows MSYS shells. On Windows the script would be called *example.bat*

SystemC TLM2.0 models can be used on Linux with gcc or on Windows with MinGW/MSys (since SystemC release v2.3.0) or MSVC 8.0. It is assumed that users of

this environment will be familiar with SystemC, TLM2.0 and will have obtained this software from www.accellera.org or similar.

## 2.4 Shared Objects and executables

The shared objects referred to in this document are either Linux shared objects, with suffix .so or Windows dynamic link libraries with suffix .dll.

The executables referred to in this document are either Linux or Windows programs and have the suffix .exe

## 2.5 Platforms, Modules and Shared Objects

Modules are created by writing scripts in tcl using iGen API calls and then running iGen to create C code which calls functions from the OP API. A Makefile is provided that will take as input the *module.op.tcl* and run iGen, gcc etc. This will then create the *model.so/.dll* shared objects.

This model.so/.dll shared object can then be simulated using the harness.exe program provided, or by writing and compiling a bespoke test harness in C.

In this document we will either use binary modules and components from the Imperas provided library, or we will provide them as source in the example directories.

# 3 Simulating Modules using harness.exe

For many platforms and modules, the *harness.exe* program will be sufficient to load and execute a simulation and it is not necessary to write your own C testbench / harness.

The *harness.exe* program is provided in the binary directory which is found, after environment initialization, on the execution PATH. To invoke the program and show the command arguments which are available, type:

```

> harness.exe --help

```

The simplest mode of invocation is to load a module and an application for the processors in the module to execute:

The argument --modulefile <filename> states which shared object module to load.

The argument --program <filename> states which application program binary to load and run on the simulated processor(s) in the module.

There are a number of examples in *Examples/PlatformConstruction* that show different modules being created and executed with *harness.exe*. Some of the examples instead create their own bespoke testbench / harness.

# 4 Imperas Simulation Overview

Before starting to create models for use with the Imperas simulation environment, you must understand how the components used in that environment interact. This section describes this in detail.

#### 4.1 Simulation Environments

There are currently two simulation environments available that can be used with models and platforms that you create:

- *OVP* allows component models created using OVP modeling technology to be used in C harness, platform and testbench files to create executables, which represent real hardware. These include processor and other behavioral components. The executable can be used to run binary application files compiled and linked for the processors whose models are included. OVP can be used in 3<sup>rd</sup> party simulation environments (for example, SystemC). It can be used to create a test harness to help validate processor models under construction, or even to create custom simulation environments. OVP has less functionality than the Imperas Professional Simulator Products in some areas and has restricted commercial usage as stipulated in the OVP click-through license agreement.

- Imperas Professional Simulator Products enhance the basic capabilities provided by OVPsim, particularly in the areas of debugger integration, tool integration and multiprocessor simulation support (including QuantumLeap parallel simulation). Contact Imperas for more information.

# 4.2 What are OVPsim and CpuManager?

OVP provides the *OVPsim* simulator and the Imperas Professional product provides the *CpuManager* simulator as dynamic linked libraries (.so suffix on Linux, .dll suffix on Windows) implementing Imperas simulation technology. The shared objects contain implementations of the OP interface functions described later in this document. The OP functions enable instantiation, interconnection and simulation of complex multiprocessor platforms using multicore processors, advanced peripheral devices and complex memory topologies.

Processor models for use with *CpuManager* and *OVPsim* are created using the *OVP Virtual Machine Interface* (VMI) API, and are available for download from the www.OVPworld.org website. This API enables the creation of processor models that run at very high simulation speeds (typically hundreds of millions of simulated instructions per second). The use of the API is described in the *OVP Processor Modeling Guide*, also available for download from the www.OVPworld.org website.

The CpuManager simulator is part of the commercial/professional product offering available from Imperas. OVPsim is the freely-available (for Non-Commercial usage) version of the simulator. The simulator can be selected at runtime by the

IMPERAS\_RUNTIME environment variable. If it is not set or is set to OVPsim the OVPsim library (which requires an OVP license) will be used. If it is set to CpuManager the CpuManager library (which requires an Imperas license) will be used.

The legacy ICM API is supported by the same products, providing a subset of the functionality offered by OP. In fact, the ICM API is implemented using OP so will be supported for the foreseeable future.

A subset of OP functionality can be used in SystemC TLM2.0. The TLM2.0 C++ interface code is available as source for processor and peripheral models, allowing the use of these models in SystemC TLM2.0 platforms.

## 4.3 Use of OP with Imperas tools

A program using the OP or ICM APIs must be linked with the Imperas RuntimeLoader library to perform runtime dynamic loading of either the CpuManager or OVPsim dynamic linked libraries, to produce a stand-alone executable. This allows the runtime selection of the CpuManager simulator for any defined platform and so enabling the use of the Imperas tools.

#### 4.4 C API and iGen

An OVP module is written in C code and compiled and linked on the host computer to produce a shared object. An OVP testbench/harness, is written in C code, compiled and linked with the *RuntimeLoader* (*libRuntimeLoader.so*) link library on the host computer to produce an executable.

iGen is a program from Imperas that can create either outline or substantially complete C code for a module or testbench/harness using a description written using iGen function calls. Use of iGen is described elsewhere and used in the examples in this document.

# 5 Separation of iGen modules and C harness / testbench

Even though both the activities of creating a design / module and creating the harness / testbench ultimately make calls into the simulators OP C API there are two distinct usage flows.

A module starts as a script as input to iGen which generates C code that makes calls to the OP API. The iGen function API and use of iGen provide a powerful and easy to use approach to building the structure of your virtual platform to be simulated.

Harnesses and testbenches are written in C and instances modules and tell the simulator how to simulate them. This can include loading programs, loading data files, setting values into registers, scheduling the execution and controlling the interaction with other simulators or with bespoke debug solutions. The OP API has been designed to provide a very efficient and powerful way to specify and control simulations.

#### For now, assume that:

module creation is done in tcl with iGen and harnesses / testbenches are written in C using the OP API.

Advanced users can use the OP calls in many different ways and can write code that will not adhere to these assumptions. For more details see the <u>Advanced Simulation Control</u> of Platforms and Modules User Guide.

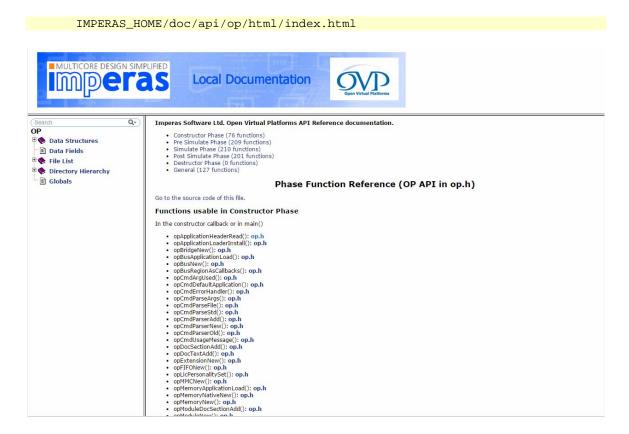

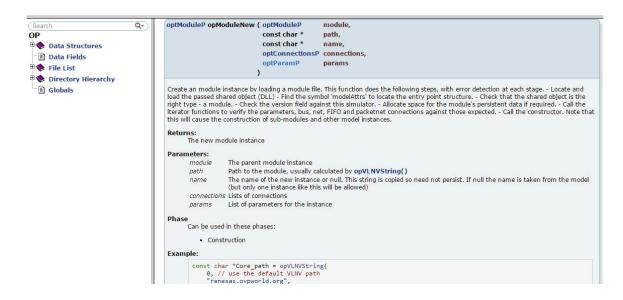

## 6 Documentation on the OP API

Provided in the installation is the online OP API Function Reference documentation. This is Doxygen-like API documentation available at:

#### It includes per function references:

# 7 Introducing a C harness / testbench

For a first example, we will introduce the simplest module and application we can and then concentrate on the harness we are going to evolve.

Take of a copy of the example, *Examples/SimulationControl/minimalHarness*:

```

> cp -r $IMPERAS_HOME/Examples/SimulationControl/minimalHarness .

> cd minimalHarness

> ls

application harness module

```

#### Examine the application source

```

> cat application/application.c

#include <stdio.h>

#include <stdlib.h>

int main(int argc, char **argv) {

printf("Hello world application\n");

return 0;

}

```

#### Compile the application

```

> make -C application

# Compiling application.c

# Linking application.OR1K.elf

```

#### Examine the module source

#### Generate the module C code and compile the module

```

> make -C module

# iGen Create OP MODULE module

# Host Compiling Module obj/Linux64/module.igen.o

# Host Linking Module object model.dll

```

If you have worked through the *iGen Platform and Module Creation User Guide* then you should be familiar with the application and simple module, filenames and use of make etc.

The most minimal test harness needs to instance a module and start simulation.

If we examine the harness in the file *harness/harness.c*, we can see it contains a *main* function:

```

int main(int argc, const char *argv[]) {

opSessionInit(OP_VERSION);

opCmdParseStd (argv[0], OP_AC_ALL, argc, argv);

optModuleP mi = opRootModuleNew(0, 0, 0);

opModuleNew(mi, "module", "ul", 0, 0);

opRootModuleSimulate(mi);

opSessionTerminate();

return 0;

}

```

It is a normal C *main()* which provides access to the command line arguments passed into the executable using argc, and argv.

The *opSessionInit()* must be at the beginning to initialize and the *opSessionTerminate()* must be at the end to terminate. These are mandatory as the first and last function calls in *main()* and must encompass all other calls to the OP API. *OP\_VERSION*, which is passed to the *opSessionInit()* call us defined in op.h and is used to verify that the API version used in this executable matches the version in the dynamically loaded simulator library.

The call to opCmdParseStd() tells the simulator to use a standard command line parser

```

opCmdParseStd (argv[0], OP_AC_ALL, argc, argv);

```

Using the command line parser allows you to put arguments on the command line to control the simulator (for example to load an application program). You may use the *--help* argument to see the supported arguments. All the available arguments are described in the Imperas Simulation Guide. It is also possible to add harness-specific arguments to the standard command line parser, this is described later.

The call to *opRootModuleNew* tells the simulator to create an empty root module and it returns a pointer 'mi' to the created module.

```

optModuleP mi = opRootModuleNew(0, 0, 0);

```

The call to opModuleNew instances a module under this root module, using the 'mi' pointer and finds the module shared object in the directory below us called 'module', and gives it the instance name of 'u1'.

```

opModuleNew(mi, "module", "u1", 0, 0);

```

Finally, we call the simulator to execute the specified root module:

```

opRootModuleSimulate(mi);

```

It is compiled and linked, using the provided Makefile, with:

```

> make -C harness

# Host Compiling Harness obj/Linux64/platform.o

# Host Linking Harness object model.dll

# Host Linking Harness harness.Linux64.exe

```

Then we can run it passing the program to be loaded for execution by the processor model in the module:

```

> harness/harness.$IMPERAS_ARCH.exe --program application/application.OR1K.elf

OVPsim started: Mon Jan 04 17:23:43 2016

Hello world application

OVPsim finished: Mon Jan 04 17:23:43 2016

```

Also, don't forget, you can pass in standard built-in command line arguments to your harness, for example enable tracing of the instruction execution:

```

> harness/harness.$IMPERAS_ARCH.exe --program application/application.OR1K.elf \

--trace --tracechange

OVPsim started: Mon Jan 04 17:23:43 2016

Info SR 00008401 -> 00008001

Info u1/cpu1', 0x0000000000000f38(_main+c): 1.sw 0x0(r1),r9

Info 'u1/cpu1', 0x000000000000f3c(_main+10): 1.movhi r3,0x0

Info R3 00000000 -> 0000493c

Info 'u1/cpu1', 0x000000000000f44(_main+18): 1.jal

0x000016fc

R9 00000fb0 -> 00000f4c

Info 'u1/cpu1', 0x0000000000000f48(_main+1c): 1.nop

Info 'ul/cpul', 0x0000000000016fc(_puts): l.addi    r1,r1,0xfffffff8

Info R1 ffffffe4 -> ffffffdc

Info SR 00008001 -> 00008401

OVPsim finished: Mon Jan 04 17:23:43 2016

```

We have provided an *example.sh* script (*example.bat* for Windows) which generates the module and compiles the application and harness.

```

> ./example.sh

```

# 7.1 Writing a harness using C++

Imperas provides a simple C++ interface to the OP API. Note that this is not a complete C++ class-based implementation, but a set of wrappers for the existing API. The interface is provided as source to be compiled with your own compiler. Source is in:

```

$IMPERAS_HOME/ImpPublic/source/host/op/op.cpp

The header is in:

$IMPERAS_HOME/ImpPublic/include/host/op/op.hpp

```

## 7.2 Naming of classes and methods.

Naming follows the scheme used in C in *op.h* e.g. the C function *opProcessorSimulate()* has in *op.hpp* the equivalent C++ method *simulate()* in the class *processor*.

## 7.3 Example

An example of a simple C++ harness is in:

```

$IMPERAS_HOME/Examples/PlatformConstruction/CPP/minimalHarness

```

Take a copy of the example

```

> cp -r $IMPERAS_HOME/Examples/PlatformConstruction/CPP/minimalHarness .

> cd minimalHarness

```

Examine the C++ harness file *harness/harness.cpp*:

```

#include <iostream>

using namespace std;

#include "op/op.hpp"

using namespace op;

int main(int argc, const char *argv[]) {

cout << "\nRunning C++ harness..." << endl;

session s;

message m;

parser p(argc, argv);

module mi;

module ul(mi, "module", "ul");

mi.simulate();

cout << "\nFinished running C++ harness." << endl;

return (m.errors() ? 1 : 0);

}</pre>

```

The source file uses the OP C++ header op/op.hpp

The OP has its own name space: op

It is necessary to construct an OP session object s to call *opSessionInit()*. An instance of the *message* class gives access to the *message* methods; it is not required for the simulator to run. Similarly, the *parser* class gives access to the *parser* methods but is only required if the parser is to be used.

Creating an instance of module *mi* without arguments creates the root module. This becomes the parent of the working modules, and is used to operate on the root module instance, calling *mi.simulate()* in this example.

To build and run the example use the command:

```

> ./example.sh

# Compiling application.c

# Linking application.OR1K.elf

rm application.o

# iGen Create OP MODULE module

# Copying STUBS module.c.igen.stubs to module.c

# Host Depending obj/Linux32/module.d

# Host Compiling Module obj/Linux32/module.o

# Host Linking Module object model.so

# Host Compiling Platform obj/Linux32/harness.o

# Host Linking Platform harness.Linux32.exe

# Host Linking Platform object model.so

Running C++ harness...

OVPsim started: Mon Feb 22 21:58:16 2016

Hello world application from C++ harness

OVPsim finished: Mon Feb 22 21:58:16 2016

Finished running C++ harness.

```

The C++ interface layer is generally complete; any OP function that does not have a C++ equivalent can be used directly; an OP pointer can be obtained using the *handle()* method from the appropriate C++ class.

# 8 The top level or root module

A root module must be created (using *opRootModuleNew*) in the main function. This root module can either:

- 1. be a self-contained single level combined harness and design by containing all the components in the system (this is how a legacy ICM platform is constructed as it has no hierarchy).

- 2. be a harness / testbench by creating an instance of the top level of the design (for example, instance a module) and supplying any testbench functionality required to run the design. In fact, it could create instances of several designs and run then independently to perform *step and compare* testing.

- 3. include both a *modelAttrs* definition, so that this module may be instanced within a higher-level design, and contain a *main* function (with a command line parser, if required) so that it can be used as a top-level design. There will be both a module shared object and a design executable created.

The test harness in the previous example (section 7 "Introducing a C harness / testbench") is about the simplest that can be created. It is in the form of the 2nd use case above: A *main()* function makes calls to the different OP simulation control capabilities.

It may be necessary to create a harness / testbench in the style of module creation using OP - i.e. as per the 3rd use case above.

We have provided the example *SimulationControl/simpleHarness* to demonstrate this approach.

All the other harnesses in this document will use the approach of not using the *modelAttrs* table, i.e. we are going to focus on the 2nd use case, where we are writing harnesses that instance other modules.

# 9 Configuring the Simulation using parameters

To increase the flexibility and reusability of a module, it can accept parameters which may be set by the module that creates the instance of this module (its parent) and whose values can be obtained by code in the module, to influence its behavior. Parameter values can be passed to its components (including sub-modules) or can influence the execution of its code. Parameter types include Boolean, Integer, Floating point and String.

#### 9.1 Parameter Lists on a Root Module

There are many parameters that are only for use with the root module and these affect the whole simulation. For example installing a ctrl-C signal handler, or suppressing the simulator's banner, or running in verbose mode. Parameters are described in the HTML documentation; go to:

```

Imperas/doc/api/op/html/index.html

```

search for '*OP\_FP\_*'. And look for parameters that must be applied to a rootmodule.

We will look at the example *Examples/SimulationControl/configureRootModule* (which is a copy of *minimalHarness* introduced above).

Take a local copy to edit:

```

> cp -r $IMPERAS_HOME/Examples/SimulationControl/configureRootModule .

> cd configureRootModule

> ls

application harness module

```

and then generate the module C code and compile and run with the provided example script:

```

> ./example.sh

```

The harness has a few extra lines of code in the *main()* to set the parameters on the creation of the root module.

We create some definitions for the root module name and the module directory name to find the module's shared object, and the instance names for the module and cpu of interest.

We can override the value of a parameter of an object before we instance it by using the correct override function for the type, for example *opParamBoolOverride* function for a Boolean type (there are functions for all the supported types). We make use of the gnu C feature of string concatenation which creates a hierarchical name string to point at the object of interest.

The definitions  $OP\_FP\_$ ' are macros to define the built-in parameters, for example  $OP\_FP\_VERBOSE$  is "verbose", so we are passing the string "verbose" as the 2nd argument and '1' (true) as the 3rd to set the simulator in verbose mode.

```

opParamBoolOverride(0, OP_FP_STOPONCONTROLC, 1);

opParamBoolOverride(0, OP_FP_VERBOSE, 1);

```

Also, for the CPU instance "u1/cpu1", we are setting the 'MIPS' rating to 200:

```

opParamDoubleOverride(mi, MODULE_INSTANCE "/" CPU_INSTANCE "/" OP_FP_MIPS,

200);

```

but note this is relative to the root module 'mi' (first argument), so we will have set "u1/cpu1/mips" to 200.

If we now build the harness:

```

> make -C harness

and run it:

```

> harness/harness.\$IMPERAS\_ARCH.exe --program application/application.OR1K.elf

We will see the simulator output will provide the verbose simulation statistics and the 'nominal MIPS' for the processor was set to 200:

```

OVPsim started: Tue Jan 12 10:48:05 2016

Info (OP_AL) Found attribute symbol 'modelAttrs' in file

'/home/graham/itest/Regression_Tests/OVPsim/Examples/OP/singletest.3095/0/module

/model.so'

Info (OP_AL) Found attribute symbol 'modelAttrs' in file

'/home/graham/Imperas/lib/Linux64/ImperasLib/ovpworld.org/processor/or1k/1.0/mod

Info (OP_AL) Found attribute symbol 'modelAttrs' in file

'/home/graham/Imperas/lib/Linux64/ImperasLib/ovpworld.org/semihosting/orlkNewlib

/1.0/model.so'

Info (OR_OF) Target u1/cpu1' has object file read from

'application/application.OR1K.elf'

Info (OR_PH) Program Headers:

Info (OR_PH) Type Offset VirtAddr PhysAddr FileSiz MemSiz

Flags Align

2000

Hello world application

Info CPU 'u1/cpu1' STATISTICS

Info Type : orlk (generic)

Info Nominal MIPS : 200

Info Final program counter: 0x1774

Info Simulated instructions: 2,112

Info Simulated MIPS : run too short for meaningful result

Info -----

Info -----

Info SIMULATION TIME STATISTICS

Info Simulated time : 0.00 seconds

User time

Info

: 0.01 seconds

Info

System time

: 0.00 seconds

Info Elapsed time

: 0.01 seconds

OVPsim finished: Tue Jan 12 10:48:05 2016

```

Now if we change the harness to remove the previous changes so that we now have the parameter to suppress the banner:

```

opParamBoolOverride(0, OP_FP_SUPPRESSBANNER, 1);

```

after we re-build the harness

```

> make -C harness

```

and then run it, we will see the output without any banner information and just see the semihosted printf from the application:

```

> harness/harness.$IMPERAS_ARCH.exe --program application/application.OR1K.elf

```

Hello world application

### 9.1.1 The available root module parameters

The complete up-to-date list of available parameters is defined in the API documentation at IMPERAS\_HOME/doc/api/op/html/index.html. Click on 'globals' in the left hand pane, then 'b' in the right hand pane, to see all the  $OP\_FP\_*$  parameters. Click on  $OP\_FP\_DEBUGPSECONSTRUCTORS$  to see the first in the list that is applicable to root modules.

Some to try out are:

```

OP_FP_FINISHTIME

OP_FP_GDBCONSOLE, OP_FP_GDBEGUI,

OP_FP_MPDCONSOLE, OP_FP_MPDEGUI,

OP_FP_SHOWBUSES, OP_FP_SHOWDOMAINS

OP_FP_WALLCLOCK, OP_FP_WALLCLOCKFACTOR

```

Most of these are set with *opParamBoolOverride*, but there are also functions to set parameters that are Enum, Int32, String, Uns32 etc.

Most of the above options are best done from the command line or from control files but can also be added to the harness if they are required permanently.

For example, to set the simulation to always run with a wallclock factor of 5x we can use OP\_FP\_WALLCLOCKFACTOR on a root module

```

opParamDoubleOverride(0, OP_FP_WALLCLOCKFACTOR, 5.0);

```

# 9.2 Using Overrides to Set parameter values on module and component instances

You can set any parameter in your design from the command line or from the C harness. It is often better to set parameters from the command line.

By using the command line --showoverrides we can see that there are some parameters on the CPU instance in the module we have instanced:

```

> harness/harness.$IMPERAS_ARCH.exe --program application/application.OR1K.elf --showoverrides

...

--override u1/cpu1/enableimperasintercepts=0 (Boolean) Enable Imperas intercepts

--override u1/cpu1/simulateexceptions=0 (Boolean) Simulate exceptions

--override u1/cpu1/trace=0 (Boolean) Enable instruction trace

--override u1/cpu1/traceshowicount=0 (Boolean) Print count with trace

--override u1/cpu1/mips=100.000000 (Double) Set the mips rate for this instance.

...

```

So we can then set some of these:

```

opParamBoolOverride(mi, MODULE_INSTANCE "/" CPU_INSTANCE "/"

OP_FP_TRACE, 1);

opParamBoolOverride(mi, MODULE_INSTANCE "/" CPU_INSTANCE "/"

OP_FP_TRACESHOWICOUNT, 1);

opParamDoubleOverride(mi, MODULE_INSTANCE "/" CPU_INSTANCE "/" OP_FP_MIPS,

200);

opModuleNew(mi, MODULE_DIR, MODULE_INSTANCE, 0, 0);

```

## 9.3 Configuring Modules and Components from Harness

In this section we will look at the use of parameters to modify the hardware definition and the component configuration from the harness.

This will use the example

\$IMPERAS\_HOME/Examples/SimulationControl/moduleParametersWithHarness

#### 9.3.1 Module Hardware Parameters

The module is the hardware definition and typically this is fixed. However, some aspects of the module may be configured using parameters when it is instanced. In this example we will configure the base address at which a peripheral model is instanced.

The parameter to be configured must be defined as a formal parameter of the module on which you wish to apply it. It may also be defined at higher levels and used to configure the lower level modules when they are instanced. The choice of where to apply the parameter depends upon the hierarchy in the design and the level at which the configuration should be made.

Defining the parameters when the module is instanced is illustrated in the topmodule (topmodule/module.op.tcl) for each of the submodules it contains

```

ihwaddformalparameter -name subUart0Address -type address iaddocumentation -name Description -text "Set base address of UART in subsystem 0" ihwaddformalparameter -name subUart1Address -type address iaddocumentation -name Description -text "Set base address of UART in subsystem 1"

```

which is used to set the configuration parameter on the module when it is instanced.

```

# configure parameters

ihwsetparameter -handle subUart0 -name baseAddress -value {subUart0Address} -

type uns64

ihwsetparameter -handle subUart1 -name baseAddress -value {subUart1Address} -

type uns64

```

In this case we are defining two formal parameters to independently set the base address for the two uarts in the sub modules, we could equally base both of the uart from a single formal parameter.

```

# configure parameters

```

```

ihwsetparameter -handle subUart0 -name baseAddress -value {subUart0Address}

-type uns64

ihwsetparameter -handle subUart1 -name baseAddress -value {subUart0Address+0x10}

-type uns64

```

We must define the formal parameter in the lowest level at which it is applied. This is shown in the submodule (submodule/module.op.tcl) in which the formal is defined

```

ihwaddformalparameter -name baseAddress -type address iadddocumentation -name Description -text "Set base address of UART"

```

and used to configure the base address at which the UART is instanced in the module.

This allows a generic module to have some configuration aspects that are defined when the hardware platform is created.

### **9.3.2** Component Feature Parameters

A peripheral or processor component model can include the behavior of different versions or types of hardware, for example a UART model can provide 16450 and 16550 behaviour. The configuration of the model can again be achieved by defining formal parameters on the model itself and then applying these in the module definition, on the command line or in the harness.

Defining the formal parameter for a peripheral model can be found in the documents  $iGen\_Peripheral\_Generator\_User\_Guide$  and  $OVP\_Peripheral\_Modeling\_Guide$  and for a processor model in the  $OVP\_Processor\_Modeling\_Guide$ .

# 9.3.3 Setting Parameters in the Harness

The harness can be used to set the parameters in modules and components using two methods.

The *opParamXXX* API functions can be used to append to a parameter list of type *optParamP* that is then passed to the module instance or the parameters can be applied directly using the OP\_PARAMS and type macros.

Note that the parameter names are the hierarchical names that are based upon the module on which they are applied.

#### 9.3.3.1 Parameter List

The following shows the parameters being applied by adding the parameters to a list

The first shows the parameter applied to the formal in the top module.

```

optParamP paramList = NULL;

// Set formal parameter on the top level module to change uart addresses

paramList = opParamUns64Set(paramList, "subUart0Address",

0x100003e8);

paramList = opParamUns64Set(paramList, "subUart1Address",

0x100003f8);

```

and the alternative is to apply directly to the sub module, rather than through the top module

```

// Set formal parameter on the top level module to change uart addresses

paramList = opParamUns64Set(paramList, "subUart0/baseAddress",

0x100003e8);

paramList = opParamUns64Set(paramList, "subUart1/baseAddress",

0x100003f8);

```

The following shows the configuration of the *outfile* parameter on the two uarts

```

// Set parameter on instance of uarts to set logfiles

paramList = opParamStringSet(paramList, "subUart0/uart0/outfile", "subUart0-

uart0.txt");

paramList = opParamStringSet(paramList, "subUart1/uart0/outfile", "subUart1-

uart0.txt");

```

Finally, the parameter list is passed to the function creating the module.

```

// instance the topmodule into the root module

opModuleNew(mi, "./topmodule", "top", 0, paramList);

```

#### 9.3.3.2 OP PARAMS Macro

Instead of creating a parameter list the configuration can be applied directly when the module is instanced using macros.

The equivalent of setting the base addresses and the uart outfiles using this method is shown below

## 9.3.4 Running Example

The example can be executed from the directory

\$IMPERAS\_HOME/Examples/SimulationControl/moduleParametersWithHarness

using the provided scripts, for example on Linux

\$ ./example.sh

```

Which will generate output similar to the following

```

```

mingw32-make: Entering directory

`C:/Imperas/Examples/SimulationControl/moduleParametersWithHarness/application'

Compiling application.c

Linking application.RISCV32.elf

rm application.RISCV32.o

mingw32-make: Leaving directory

`C:/Imperas/Examples/SimulationControl/moduleParametersWithHarness/application'

mingw32-make: Entering directory

`C:/Imperas/Examples/SimulationControl/moduleParametersWithHarness/submodule'

# iGen Create OP MODULE module.c.igen.stubs

# No Update to existing module.c. Compare with module.c.igen.stubs if changes

made to iGen file module.op.tcl

# Host Depending obj/Windows64/module.d

mingw32-make: Leaving directory

`C:/Imperas/Examples/SimulationControl/moduleParametersWithHarness/submodule'

mingw32-make: Entering directory

`C:/Imperas/Examples/SimulationControl/moduleParametersWithHarness/submodule'

# No Update to existing module.c. Compare with module.c.igen.stubs if changes

made to iGen file module.op.tcl

# Host Compiling Module obj/Windows64/module.o

# Host Linking Module object model.dll

mingw32-make: Leaving directory

`C:/Imperas/Examples/SimulationControl/moduleParametersWithHarness/submodule'

mingw32-make: Entering directory

`C:/Imperas/Examples/SimulationControl/moduleParametersWithHarness/topmodule'

# iGen Create OP MODULE module.c.igen.stubs

# No Update to existing module.c. Compare with module.c.igen.stubs if changes

made to iGen file module.op.tcl

# Host Depending obj/Windows64/module.d

mingw32-make: Leaving directory

`C:/Imperas/Examples/SimulationControl/moduleParametersWithHarness/topmodule'

mingw32-make: Entering directory

`C:/Imperas/Examples/SimulationControl/moduleParametersWithHarness/topmodule'

# No Update to existing module.c. Compare with module.c.igen.stubs if changes

made to iGen file module.op.tcl

# Host Compiling Module obj/Windows64/module.o

# Host Linking Module object model.dll

mingw32-make: Leaving directory

`C:/Imperas/Examples/SimulationControl/moduleParametersWithHarness/topmodule'

mingw32-make: Entering directory

`C:/Imperas/Examples/SimulationControl/moduleParametersWithHarness/harness'

# Host Depending obj/Windows64/harness.d

mingw32-make: Leaving directory

`C:/Imperas/Examples/SimulationControl/moduleParametersWithHarness/harness'

mingw32-make: Entering directory

`C:/Imperas/Examples/SimulationControl/moduleParametersWithHarness/harness'

# Host Compiling Harness obj/Windows64/harness.o

```

```

# Host Linking Harness harness.Windows64.exe

mingw32-make: Leaving directory

`C:/Imperas/Examples/SimulationControl/moduleParametersWithHarness/harness'

CpuManagerMulti (64-Bit) v20190225.0 Open Virtual Platform simulator from

www.IMPERAS.com.

Copyright (c) 2005-2019 Imperas Software Ltd. Contains Imperas Proprietary

Information.

Licensed Software, All Rights Reserved.

Visit www.IMPERAS.com for multicore debug, verification and analysis solutions.

CpuManagerMulti started: Mon Mar 18 16:16:35 2019

Info (HARNESS) Define parameters using optParamP parameter list

Info (HARNESS) Set formal parameters on submodule

Writing to UARTs - see log files

CpuManagerMulti finished: Mon Mar 18 16:16:35 2019

CpuManagerMulti (64-Bit) v20190225.0 Open Virtual Platform simulator from

www.IMPERAS.com.

Visit www.IMPERAS.com for multicore debug, verification and analysis solutions.

-- subUart0-uart0.txt contents --

Hello UARTO world

-- subUart1-uart0.txt contents --

Hello UART1 world

Press any key to continue . . .

```

The way in which the configuration is applied can be modified in the harness and topmodule to show the different configuration options described earlier.

In the top of harness/harness.c there are three defines

```

// Set the defines to show alternate ways of setting parameters

#define PARAMLIST

//#define TOPLEVEL

// Define separate formal parameters for each sub module uart (set dualbase in topmodule/module.op.tcl)

#define DUALBASE

```

PARAMLIST when defined will use the list defined by optParamP to set parameters, otherwise the OP\_PARAMS macros will be used.

TOPLEVEL can only be defined when PARAMLIST is defined and will set the parameters on the top level module

DUALBASE requires that the variable *dualbase* in *topmodule/module.op.tcl* is also set. This controls whether the uart base addresses are both set or uart1 base address is set relative to uart0.

## 9.4 Special parameter values

Certain parameters are handled specially by the simulator. These are described in the following sections.

## 9.4.1 MIPS parameter

All processors support a double parameter called *mips*, used to specify *the nominal processor speed in millions of instructions per second*. This nominal mips rate is used to apportion run time between processors in a multiprocessor simulation. The default nominal mips rate for each processor is 100. The section above shows an example of using a hierarchical parameter setting to configure a processor with a nominal mips rate of 200 MIPS instead.

```

opParamDoubleOverride(mi, MODULE_INSTANCE "/" CPU_INSTANCE "/" OP_FP_MIPS,

200);

opModuleNew(mi, MODULE_DIR, MODULE_INSTANCE, 0, 0);

```

## 9.4.2 Endian parameter

The model documentation for processors includes a definition of the endianness supported by that processor. This may be *big*, *little* or *either*.

If the endian is defined as *either* then the model will accept a user string attribute called *endian*, used to specify the endianness of the processor. The *endian* attribute may take the values *big* or *little*.

Some processors allow the endianness to be changed dynamically by software. The *endian* attribute only sets the initial value for the endianness at the start of simulation in this case.

You could set the endianness in the instantiation of the processor, or you could set it in the testbench with a hierarchical parameter setting e.g.:

Note that the OR1K used in this example does not support the endian parameter.

# 9.5 Common error messages related to parameters

Some of the common errors are:

# Error (OP\_PNF) Parameter '<hier param name>' has no formal parameter defined in the model.

You are trying to call one of the parameter setting functions and the parameter you have specified has not been found - reasons are often spelling mistakes or wrong level of hierarchy. Use the command line argument --showoverrides or the root module parameter  $OP\_FP\_SHOWFORMALS$  to get a list of all the possible parameters in your design that can be set.

# Error (OP\_DCE) <hier param name> cannot be converted from a double to a boolean

You are setting the value of a parameter to an illegal value - for example opParamDoubleSet needs the value to be a double etc. - so ensure the correct function is used, e.g. opParamBoolSet, opParamDoubleSet etc. and that it matches with the value set.

# 10 Controlling the simulation using the Command Line

When using a testbench or harness we will want to control the simulation from the command line, pass in arguments to configure the simulation, and set other parameters that will change the simulation run.

There are OP functions that we can use in our harness that will provide different sets of command line arguments. There is the option of basic or full commands, and you can extend the command line parser with your own command line arguments.

It is also possible to pass arguments from the simulator command line into the *main()* of applications running on simulated processors.

## 10.1 standardCommandLineParser example

Let's start with a Command Line Parser (CLP), this is the standard command line parser that could be used to add custom arguments. It is configured to include all standard arguments.

If we have a look at the example (which is a copy of *minimalHarness* introduced above) by making a local copy to edit:

```

> cp -r $IMPERAS_HOME/Examples/SimulationControl/standardCommandLineParser .

> cd standardCommandLineParser

> ls

application harness module

```

There are two places that are related to the CLP in *harness/harness.c*:

```

static void cmdParser(optCmdParserP parser) {

}

```

and in main():

```

optCmdParserP parser = opCmdParserNew(HARNESS_NAME, OP_AC_ALL);

cmdParser(parser);

opCmdParseArgs(parser, argc, argv);

```

and we can compile and run as normal using the provided example script. This time we have put a '--help' in the example script so we can see what command line arguments the simulator is allowing:

```

> ./example.sh

```

and we will see the full set of allowed options - this is due to the choice of  $OP\_AC\_ALL$  in the opCmdParserNew call creating the parser.

If we change this to OP\_AC\_NONE, or OP\_AC\_BASIC and run the example script we will see that we get only very basic arguments allowed. Note you get an error with this basic level of the command line parser because the argument --program is not allowed! This choice would be useful when you want to control the usage of your harness/system such that users could only use the built in programs etc. This would be used when you are defining and using your own arguments.

A more useful set would be: *OP\_AC\_SIM*.

To see a full list, use --help with either your own harness/platform or the provided simulators: harness.exe, iss.exe etc. To get a more detailed explanation of the different arguments, please read the Control File User Guide.

The above example has shown the creation of a new command line parser using a call to the function op CmdParserNew which returns a parser object parser. This object can be used to add new command line arguments before the command line is processed with calls to *opCmdParseArgs*.

When you do not wish to add new custom command line arguments, i.e. you only want the standard command line arguments provided by the simulator, the function opCmdParseStd can be used in place of the above two functions as shown below

```

int main (int argc, const char *argv[]) {

opCmdParseStd(argv[0], OP_AC_SIM, argc, argv);

```

The first argument is used in messages and can be the name of the program, argv[0], as shown or can be any constant string. The second argument controls the arguments that will be available.

# 10.2 Verbose Output

When verbose output is selected output is generated at the end of simulation giving statistics about the number of instructions executed by each processor, the simulated MIPS rate for each processor, and the total instructions and MIPS rate. This information is present when --verbose is specified on the command line.

The actual performance reported may vary and depends on the performance of the native host. In a typical example the overall simulation speed is apportioned across each processor based upon the nominal MIPS rate configured for each processor.

#### 10.2.1 Simulation Time Statistics

In verbose mode the simulator writes information about simulated and elapsed time. Four time values appear in the SIMULATION TIME STATISTICS paragraph:

simulated time is the duration of the simulation in simulated time. This corresponds exactly to the notion of time in a simulation language such as Verilog and VHDL; it is entirely unrelated to wall-clock time.

wser time is the time that the simulation process spent executing instructions on the host machine; system time is the time the host machine spent in the system while executing instructions on behalf of the simulation process. Elapsed time is the overall time taken by the simulation process on the host from start to finish. All three of these times will vary from run to run, depending on the host load average and other factors. Real time ratio shows how much faster than real time this simulation ran.

For each processor, the *simulated MIPS* line gives the rate at which instructions for that processor were executed in *wallclock* time. In other words, the simulated MIPS number for a processor is calculated by dividing the number of instructions executed by that processor by the elapsed time for the simulation process. In this example, the reported simulated MIPS for *cpu1* is calculated by dividing the simulated instructions (1,658,997,966) by the elapsed time (2.12 seconds) to give 781.2:

```

Info CPU 'cpul' STATISTICS

Info Type : or1k

Info Nominal MIPS : 100

Info Final program counter : 0x1dcc

Info Simulated instructions: 1,658,997,966

Info Simulated MIPS : 781.2

```

Provided that a processor does not halt during a simulation, then the simulation ran faster than real time if simulated MIPS exceeds nominal MIPS, and slower than real time if nominal MIPS exceeds simulated MIPS.

When optimizing an application, you should be looking at and minimizing simulated time. When optimizing a model for efficiency, you should be looking at elapsed time.

# 10.3 Passing arguments into application programs

When running a simulation it is often useful to be able to pass arguments into the *main()* of the application running on the simulated processor.

Take a copy of the example

```

> cp -r $IMPERAS_HOME/Examples/SimulationControl/passingArgvIntoApplications .

> cd passingArgvIntoApplications

```

And examine the application file *application/application.c*:

This shows that the application is expecting and testing for arguments to be passed into it.

If we run without passing in any arguments, as performed in the standard script, we get:

```

> ./example.sh

OVPsim started: Tue Jan 5 13:53:17 2016

Passing argument into application. (no args) num(10)

OVPsim finished: Tue Jan 5 13:53:17 2016

```

We can pass arguments from the simulator command line to the application *argv* with the simulator's --*argv* command line argument.

Any arguments on the *example.sh* command line are passed to the harness executable command line in the script, so we can add additional arguments to the harness as shown:

```

> ./example.sh --argv 21

OVPsim started: Tue Jan 5 13:53:17 2016

Passing argument into application. (Got an Arg) num(21)

OVPsim finished: Tue Jan 5 13:53:17 2016

```

Two important things to note:

- The --argv argument MUST BE THE LAST SIMULATOR ARGUMENT ON THE COMMAND LINE as all arguments following it are passed down to all the processors applications without further processing

- The semihost libraries for some processors do not support this feature (most do support this feature)

# 10.4 Use of debugging options

There are many different standard debugging options and they are discussed in detail in the various provided debugger documents.

There are options related to *GDB*, for example:

```

--gdbconsole

Pop up gdb(s) in console window(s)

[platform]

--gdbegui

[platform] Start qdb debug in Eclipse (eGui)

--gdbflags

Pass additional flags to a gdb e.g.

strings

des/cpu1=special_flag

--gdbinit

strings

Pass a file to the gdb to execute

before the prompt is displayed

--qdbpath

Set the gdb path for a processor. e.g.

strings

des/cpul=/usr/bin/orlk/gdb

```

and MPD (these are only available in the Imperas simulator, not OVPsim):

#### and eGui:

```

--eguioptions string Pass these options onto the command line of GUI when started --eguicommands string Pass these commands to the GUI at startup

```

Please use the --help option on your harness or one of the simulators or look in the Control File User Guide.

For more information on tracing, please see the section on tracing below.

## 10.5 Adding harness specific command line options

Often you want to add your own arguments to control a simulation, setting options, providing filenames, etc.

It is easy to use the standard argument parser and to augment it with your own arguments and use them in your harness.

#### **NOTE**

It is recommended that all new arguments are added using only lower case characters, for example add an argument as '--mynewargument' rather than using '--myNewArgument'. Although upper case characters can be used they are converted internally to lower case to prevent problems when moving between different host machine operating systems.

Take a local copy to edit:

```

> cp -r $IMPERAS_HOME/Examples/SimulationControl/addingNewCommandLineArguments .

> cd addingNewCommandLineArguments

```

If we look at *harness/harness.c* we see we added some storage to hold the values of our new arguments:

```

} options = {

.myarg = 0,

.newString = NULL,

};

```

We add the new arguments to the *cmdParser* function using calls to *opCmdParserAdd* to define them:

and we have defined a bool argument --myarg, with a short version --m, and will put its value into options.myarg.

We have also declared a string argument --newstring and will hold its value in options.newString.

They have both been given the group name 'myargs group' for grouping in the --help listing.

We have added a new function to check the status of the arguments:

```

static void cmdParserCheck(optCmdParserP parser) {

if (!opCmdArgUsed (parser,"program")) {

opMessage("F", HARNESS_NAME, "Argument '--program' must be specified");

}

if (options.myarg) {

opMessage("I", HARNESS_NAME, "Argument 'myarg' selected (%d)",

options.myarg);

}

if (options.newstring) {

opMessage("I", HARNESS_NAME, "Argument 'newstring' selected (\"%s\")",

options.newString);

}

}

```

and to print out their status. Note that we are also now forcing the rule that the --program argument must be specified.

And in the main function we now have the following that relates to the command line parser:

```

optCmdParserP parser = opCmdParserNew(HARNESS_NAME, OP_AC_ALL);

cmdParser(parser);

if (!opCmdParseArgs(parser, argc, argv)) {

```

```

opMessage("E", HARNESS_NAME, "Command line parse incomplete");

}

cmdParserCheck(parser);

```

If we now run:

```

./example.sh

```

We see nothing from the arguments as the script is applying the minimum argument --program that we require, but if we just invoke the harness executable:

Of course, now that the values are in C in your harness, you can use them as controlling parameters on modules, processors etc.

## 10.5.1 Argument Conflicts

The command line parser module checks for duplicate commands at runtime. This mechanism will detect if the user's argument names clash with each other or with built in arguments. If this happens and you get the error message as shown below indicating you need to use a different name.

```

Error (CM_DF) This program is trying to install command line flag 'verbose' which is already in use.

Please study the list below then select another name.

flag short argument description

...

```

# 10.6 Other useful command line options

Some of the most useful command line options not already discussed are listed here:

There are a list of 'show' commands used to give visibility of the contents of a design, the commands available, and the contents of a library :

To show design information of the loaded design

```

--showbuses [root] List all (static) bus connections

--showdomains [root] List the (initial) state of each memory domain

```

To show system, model and other parameters than can be changed in the system, on the command line before the simulation start

```

--showmodeloverrides [root] List overrides requested by models in the platform

--showoverrides [root] List all possible platform overrides

--showsystemoverrides [root] List overrides in the platform provided by the simulator

```

To show commands that are available in the design that can be called

```

--showcommands [root] List commands that can be called with -- callcommand

```

To show system environment variables that may be set to control operations of the simulator

```

--showenvvars List all environment variables read by Imperas products

```

To show a list of items in the VLNV library (set by the IMPERAS\_VLNV environment variable):

```

--showlibraryextensions Semihost and other intercept libraries

--showlibrary All models and platforms

--showlibrarymmcs Memory model components (caches)

--showlibrarymodules Modules

--showlibraryperipherals Peripherals

--showlibraryplatforms Platform executables

--showlibraryprocessors Processor models

```

To convert warnings to errors so that simulation cannot continue past a message at a Warning level

```

--werror

```

To modify the interaction between the user and the simulation or between components in the simulation

```

--quantum

--timeprecision

--wallclockfactor

```

To control how long the simulation will run

```

--finishafter, --finishtime

```

To automatically install a ctrl-C handler into the simulation platform

#### --stoponcontrolc

For complete information on these and other arguments please see the explanation in the Control File User Guide.

# 11 Writing your own harness.exe

As a more complete example, let's walk through the code that we used to implement *harness.exe*. We have provided it as an example, so you can understand it and also so you can copy it and use it as the basis for other bespoke harnesses.

```

> cp -r $IMPERAS_HOME/Examples/SimulationControl/dynamicHarness .

> cd dynamicHarness

```

The module and application are the same as those used in the *simpleHarness* example, so we will just look here at the file *harness/harness.c*.

The example uses the first style of a test harness as described in section 8 in that it does not use an *attrsTable* and makes OP calls from the *main* function.

It adds commands to the command line parser to allow user selection of a module shared object either from a VLNV path or from a direct path.

So here is the full file, interspersed with some explanations of some of the more pertinent sections.

```

#include <stdio.h>

#include <string.h>

#include <stdlib.h>

#include "op/op.h"

```

Declare some type definitions to hold the data:

Provide some extra help information in a string:

```

harness.exe --modulevendor <vendor> --modulelibrary <library> --

modulename <name> "

" --version <version>\n"

"To execute a platform from a local directory:\n"

harness.exe --modulefile <file>\n"

"To see the parameters that can be overridden platform:\n"

harness.exe --modulefile <file> --showoverrides \n"

"To trace instructions:\n"

--trace\n"

"To use the graphical debugger:\n"

--mpdegui\n"

"To see more output:\n"

--verbose\n"

"Examples:\n"

" harness.exe --modulevendor arm.ovpworld.org --modulename ARMv8-A-

FMv1\n"

"or harness.exe --modulefile mymodule." IMPERAS_SHRSUF "\n";

```

Provide a function used when we have any errors and we want to end the simulation:

```

static void exitWithErrors(void) {

opSessionExit(1);

}

```

Provide a function to test for an environment variable being present and if not increment an error variable:

```

static Uns32 errors = 0;

static void reportEnvironment(const char *program, const char *variable) {

if(!getenv(variable)) {

printf("%s: Please set environment variable '%s'\n", program, variable);

errors++;

}

}

```

Provide a function that will check for all the required environment variables and exit if any are not found:

```

static void checkEnvironment(const char *program) {

reportEnvironment(program, "IMPERAS_HOME");

reportEnvironment(program, "IMPERAS_VLNV");

if(errors) {

exit(1);

}

}

```

The main function:

```

int main(int argc, const char **argv) {

checkEnvironment(argv[0]);

opSessionInit(OP_VERSION);

```

Use the standard command parser with the simulation and library options:

```

optCmdParserP parser = opCmdParserNew(argv[0], OP_AC_SIM | OP_AC_LIB);

```

provide an extra user message to the command line parser that will be appended at the end of the *-help* output:

```

opCmdUsageMessage(parser, helpMessage);

```

initialize our data structures to default values:

```

modelSpec model = { .vlnv={0, "module", 0, "1.0"}, .file=0,

.parameters=NULL, .instcount=1};

```

add extra command line arguments, defining their type, values, groups, etc.:

```

opCmdParserAdd (parser, "modulevendor", "V", 0, " harness",

OP_FT_STRINGVAL, \

&model.vlnv.vendor, "Module vendor",

OP_AC_ALL,

opCmdParserAdd (parser, "modulelibrary", "L", 0, " harness",

OP_FT_STRINGVAL, \

&model.vlnv.library, "Module library (not usually required)", OP_AC_ALL,

opCmdParserAdd (parser, "modulename",

"N", 0, " harness",

OP_FT_STRINGVAL, \

&model.vlnv.name, "Module name",

OP_AC_ALL,