# iGen Platform and Module Creation User Guide

This document describes the use of the Imperas Model Generator *iGen* to create a virtual platform using OVP APIs.

# Imperas Software Limited

Imperas Buildings, North Weston, Thame, Oxfordshire, OX9 2HA, UK docs@imperas.com

| Author:     | Imperas Software Limited                         |

|-------------|--------------------------------------------------|

| Version:    | 2.1.1                                            |

| Filename:   | iGen_Platform_and_Module_Creation_User_Guide.doc |

| Last Saved: | Tuesday, 02 June 2020                            |

| Keywords:   | iGen Platform and Module Creation User Guide     |

# **Copyright Notice**

Copyright © 2020 Imperas Software Limited All rights reserved. This software and documentation contain information that is the property of Imperas Software Limited. The software and documentation are furnished under a license agreement and may be used or copied only in accordance with the terms of the license agreement. No part of the software and documentation may be reproduced, transmitted, or translated, in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without prior written permission of Imperas Software Limited, or as expressly provided by the license agreement.

#### Right to Copy Documentation

The license agreement with Imperas permits licensee to make copies of the documentation for its internal use only. Each copy shall include all copyrights, trademarks, service marks, and proprietary rights notices, if any.

#### **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

#### Disclaimer

IMPERAS SOFTWARE LIMITED., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

# Table of Contents

| 1                                              | Preface |                                                   |      |

|------------------------------------------------|---------|---------------------------------------------------|------|

|                                                | 1.1     | Notation                                          | 6    |

|                                                | 1.2     | Related Documentation                             | 6    |

|                                                | 1.3     | Glossary / Terminology                            | 7    |

| 2                                              | Intro   | oduction                                          | 9    |

|                                                | 2.1     | Prerequisites                                     | 9    |

|                                                | 2.2     | Obtaining & installing iGen                       | 9    |

|                                                | 2.3     | Compiling Examples described in this Document     | 9    |

|                                                | 2.4     | Shared Objects and executables                    | 10   |

|                                                | 2.5     | Platforms, Modules and Shared Objects             | 10   |

|                                                | 2.6     | Simulating Modules using harness.exe              | 10   |

|                                                | 2.7     | Writing a bespoke C test harness                  | 11   |

| 3                                              | Desc    | cribing a hardware design (a virtual platform)    | 12   |

|                                                | 3.1     | Design hierarchy                                  | 12   |

| 4                                              | Crea    | ting and simulating a first virtual platform      | 14   |

|                                                | 4.1     | A quick run through                               |      |

|                                                | 4.2     | The simple application - Hello World              |      |

|                                                | 4.2.1   | How printf works using semihosting                | . 16 |

|                                                | 4.3     | Defining the platform using iGen                  | 16   |

|                                                | 4.3.1   |                                                   |      |

|                                                | 4.3.2   | 8                                                 |      |

|                                                | 4.3.3   | 8 · F                                             |      |

|                                                | 4.3.4   |                                                   |      |

|                                                | 4.3.5   | $\mathcal{E}$ 1 $\mathcal{E}$                     |      |

|                                                | 4.3.6   |                                                   |      |

|                                                | 4.4     | Running iGen                                      |      |

|                                                | 4.5     | iGen generated module files                       | 19   |

|                                                | 4.6     | Running the simulation using harness.exe.         | 19   |

|                                                | 4.6.1   |                                                   | 20   |

| 5 Creating a module with a peripheral (a UART) |         |                                                   | 21   |

|                                                | 5.1     | Module overview                                   |      |

|                                                | 5.2     | Quick run through                                 |      |

|                                                | 5.3     | The application - writing to the UART             |      |

|                                                | 5.4     | Defining the platform using iGen                  |      |

|                                                | 5.4.1   | $\mathcal{C}$                                     |      |

|                                                | 5.4.2   |                                                   |      |

|                                                | 5.4.3   |                                                   |      |

|                                                | 5.4.4   | Full iGen listing for simpleCpuMemoryUart module  | 25   |

|                                                | 5.5     | Running iGen                                      |      |

|                                                | 5.6     | Running the simulation using harness.exe          |      |

|                                                | 5.6.1   |                                                   |      |

| 6                                              |         | nging the processor being used (From OR1K to ARM) | 29   |

| 7                                              | Add     | ing Bus Bridges, Aliasing address regions         | 31   |

| 7.1    | Static Bus bridges                                     | 31 |

|--------|--------------------------------------------------------|----|

| 7.1    | .1 Aliasing                                            | 32 |

| 7.2    | Dynamic Bus Bridges                                    | 34 |

| 7.2    | .1 Introduction                                        | 34 |

| 7.2    | .2 Running the simulation                              | 36 |

| 8 Byt  | te Swapping (Endian Correction)                        | 39 |

| 8.1    | Bus Connections                                        | 39 |

| 8.2    | Performance considerations                             | 40 |

| 9 Tw   | o processors with shared memory                        | 42 |

| 9.1    | Adding Hardware Elements                               | 42 |

| 9.2    | Making Connections                                     |    |

| 9.3    | The example encrypt and decrypt applications           | 45 |

| 9.4    | Running the Example                                    | 48 |

| 10 Cad | ches (using Memory Model Components (MMC))             | 50 |

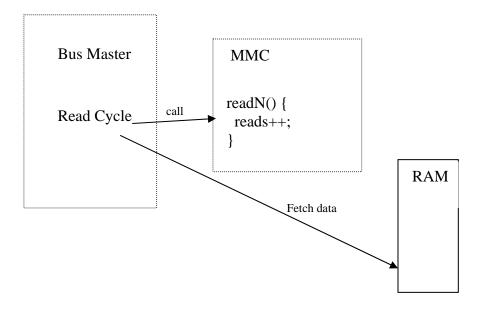

| 10.1   | Transparent or Full MMC Models                         | 50 |

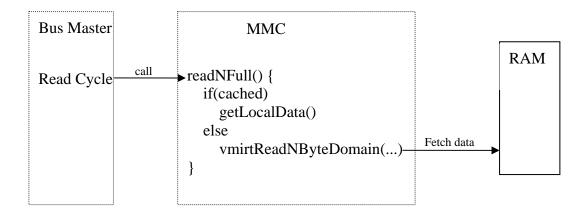

| 10.2   | MMC Operation                                          | 51 |

| 10.    | 2.1 Transparent Model                                  | 51 |

| 10.    | 2.2 Full Model                                         | 52 |

| 10.3   | Creating and connecting an MMC                         | 52 |

| 10.    | 3.1 Transparent MMC Example                            | 52 |

| 10.    | 3.2 Full MMC Example                                   | 54 |

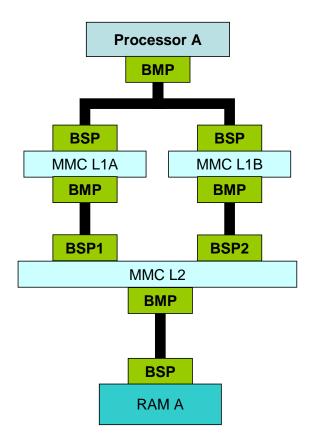

| 10.    | 3.3 Cascaded MMC Example                               | 56 |

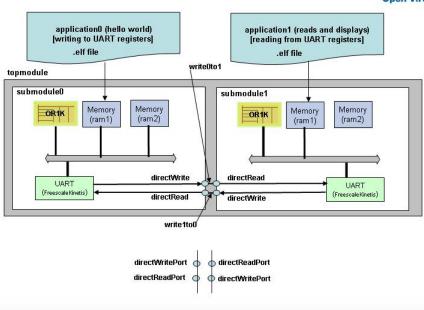

| 11 Usi | ng Module Hierarchy in Virtual Platforms               | 61 |

| 11.1   | A two level platform: simpleHierarchy                  | 61 |

| 11.2   | Creating the sub module                                | 62 |

|        | 2.1 Compiling the submodule                            |    |

| 11.3   | Creating the top module                                | 63 |

| 11.    | 3.1 Instancing a sub module                            | 63 |

| 11.    | 3.2 Compiling the topmodule                            |    |

| 11.4   | $\mathcal{E}$                                          |    |

| 11.5   | Application1 - reading from the UART                   |    |

| 11.6   | Running the hierarchical platform simulation           |    |

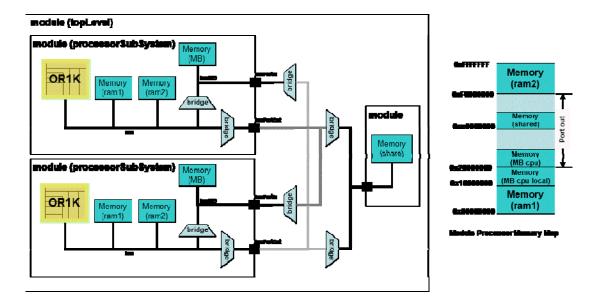

| 12 Hie | erarchy and Connectivity in Modules                    |    |

| 12.1   | The top level                                          |    |

| 12.2   | The processor sub system                               |    |

| 12.3   | The memory sub system                                  |    |

| 12.4   | The Test Application                                   |    |

| 12.5   | Building the Example                                   |    |

| 12.6   | Running the simulation                                 |    |

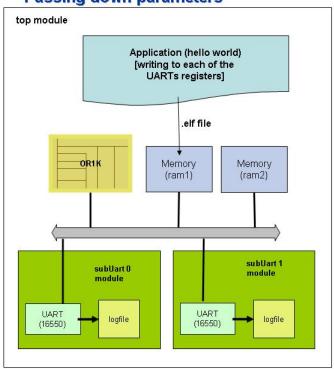

|        | sing Parameters down module hierarchy                  | 73 |

| 13.1   | Creating the sub module                                |    |

| 13.2   | Creating the top module                                |    |

| 13.3   | The application                                        |    |

| 13.4   | Running the simulation                                 |    |

|        | ectory structure: VLNV or direct paths                 | 78 |

| 14 1   | A hierarchical design using a VLNV directory structure | 78 |

# iGen Platform and Module Creation User Guide

| 14.2   | The directory structure                             | 79 |

|--------|-----------------------------------------------------|----|

| 14.3   | Changing the controlling scripts                    | 79 |

| 14.4   | The module instances                                | 80 |

| 15 Lo  | pading programs into the design                     | 81 |

| 16 Lo  | pading symbols into the simulator                   | 82 |

| 17 Set | etting Model Parameters                             | 83 |

| 18 Ad  | dvanced Information & Usage of iGen                 | 84 |

| 18.1   | Overview of detailed platform construction          | 84 |

| 18.    | 3.1.1 Harnesses and Modules                         | 84 |

| 18.    | 3.1.2 The contents of a module                      | 84 |

| 18.    | 3.1.3 The Contents of a Harness or Test Bench       | 85 |

| 18.    | 3.1.4 Module Parameterization                       | 86 |

| 18.    | 3.1.5 Efficiency                                    | 87 |

| 18.2   | Order of Platform construction                      | 87 |

| 18.3   | Editing the C of a module                           | 87 |

| 18.4   | Writing out a testbench / harness                   | 88 |

| 19 iGe | en Module related Error Messages                    | 89 |

| 20 (De | Deprecated) Creating ICM platforms with iGen        | 90 |

| 20.1   | Generated files                                     | 90 |

| 20.    | .1.1 User file: platform.c                          | 90 |

| 20.    | .1.2 Constructor file: platform.constructor.igen.h  | 91 |

| 20.    | .1.3 Options file: platform.options.igen.h          | 91 |

| 20.    | .1.4 Handles file: platform.handles.igen.h          | 91 |

| 20.    | .1.5 Command line parser file: platform.clp.igen.h. | 91 |

| 20.2   | Repeated use of iGen                                | 91 |

| 20.3   | Adding a copyright header                           | 91 |

| 20.4   | Checking the Platform                               | 91 |

#### 1 Preface

The Imperas simulators can use models described in C or C++ and the models can be exported to be used in simulators and platforms using C, C++, SystemC or SystemC TLM2.

This document describes the use of the iGen Model Generator, which executes scripts making calls to the iGen Command API. The scripts use TCL (Tool Control Language) as input and iGen creates C templates for simulation models and plugins, and creates interfaces for SystemC TLM2 simulation and creates virtual platforms, testbenches and modules using the OP C API and SystemC TLM2.

This document specifically describes how iGen is used to create platforms and modules for use with Imperas and OVP virtual platform simulators and tools.

#### 1.1 Notation

Text representing code, a command or output from *iGen* or other

program.

*keyword* A word with special meaning.

#### 1.2 Related Documentation

There are several documents available as PDF:

**Getting Started**

• Imperas Installation and Getting Started Guide

Interface and API

- OVP Peripheral Modeling Guide

- OVPsim Using OVP Models in SystemC TLM2.0 Platforms

References to specific uses of iGen

- iGen Model Generator Introduction

- iGen Platform and Module Creation User Guide

- Imperas Peripheral Generator Guide

Usage of Modules and Peripherals created using iGen

- Simulation Control of Platforms and Modules User Guide

- Advanced Simulation Control of Platforms and Modules User Guide

Also, in your installation there is the online iGen Function API Command reference documentation. This is Doxygen-like API documentation available at:

IMPERAS\_HOME/doc/api/igen/html/index.html

#### For example:

#### 1.3 Glossary / Terminology

**OP API** - OVP Platforms API - C API used for creating and controlling virtual platforms. 2nd generation API, replaces ICM API. iGen creates modules/platforms in C using this API.

**iGen** - Imperas productivity tool that has a powerful script based function API that is used to create C/C++/SystemC models and templates. Described in the iGen Model Generator Introduction, and for platforms, in the iGen Platform and Module Generator User Guide.

**OVPsim** - Simulator for Open Virtual Platforms that executes platforms and models coded in the OVP APIs.

**CpuManager** - Imperas commercial simulator that executes platforms and models coded in the OVP APIs.

**Platform / Module** (used interchangeably) - a collection of components connected together into a level of hierarchy in a system to be simulated. This is a program in C/C++ making calls into OP API and normally compiled into a shared object/dynamically linked library and loaded by the simulator at run time.

**Testbench / Harness** - program in C/C++ making calls into OP API to connect and control OVP components. Normally linked to the simulator to provide an .exe binary that can be executed. Used to instantiate one or more platforms/modules and controls their execution. The main difference, from a platform/module, is that a testbench or harness

includes a call to the function main(), may include a command line parser and is linked to create an executable binary (.exe) file.

**Root Module** - used to describe the initial platform/module that instantiates one or more platforms/modules and controls their execution. Used in the testbench/harness.

#### 2 Introduction

Imperas simulation technology enables very high performance simulation, debug and analysis of platforms containing multiple processors and peripheral models. The technology is designed to be extensible: you can create your own platforms, new models of processors, and other platform components using interfaces and libraries supplied by Imperas. Platform models developed using this technology can be used both with Imperas simulation products and the freely-available OVPsim platform simulator.

iGen is an Imperas productivity tool that has a powerful script based function API that is used to create C/C++/SystemC platform models and component templates.

#### 2.1 Prerequisites

Since models and platforms for use with Imperas and OVP tools are written in C, an important prerequisite is that you must be proficient in the C language.

iGen uses the TCL scripting language, so it is beneficial to have some basic understanding of TCL.

#### 2.2 Obtaining & installing iGen

iGen is available as part of the Imperas DEV and SDK packages. So it is assumed you have downloaded one of these from the Imperas website and have installed it on the host machine.

## 2.3 Compiling Examples described in this Document

The examples use processor and component models and toolchains, available to download from the www.OVPworld.org website or as part of an Imperas installation.

The compilation of the examples makes use of Makefiles and GNU make. The instructions indicate the use of the command *make* on Linux systems and MinGW *mingw32-make* command on Windows systems.

The Makefiles referred to in this document are written for GNU make. Standard Makefiles supplied by Imperas support compilation and linking using GNU tools on both Windows and Linux.

Example scripts will be referred to, for example, as *example.sh*. The shell (extension *sh*) script files may be used on Linux and in Windows MSYS shells. The batch (extension *bat*) files may be used in Windows Explorer or in a Windows command shell.

SystemC TLM2.0 models can be used on Linux with gcc or on Windows with MinGW/MSys (since SystemC release v2.3.0) or MSVC (Imperas/OVP has been used with version MSVC 8.0). It is assumed that users of this environment will be familiar with SystemC, TLM2.0 and will have obtained this software from www.systemc.org or similar.

#### 2.4 Shared Objects and executables

The shared objects referred to in this document are either Linux shared objects, with suffix .so or Windows dynamic link libraries with suffix .dll.

The executables referred to in this document are either Linux or Windows programs and both have the suffix .exe

#### 2.5 Platforms, Modules and Shared Objects

Modules are created by writing scripts using iGen API calls and then using iGen to generate C code that calls functions from the OP API. A Makefile is provided that will take as input a file *module.op.tcl* and execute iGen and the host compiler and linker to create the *model.so/.dll* shared objects.

The *model.so/.dll* shared object can then be loaded and simulated using the *harness.exe* program (provided in the installation binary directory), or by writing a bespoke test harness in C using the OP API.

#### 2.6 Simulating Modules using harness.exe

For most simple iGen constructed platforms and modules the harness.exe program can be used.

To see the commands that can be used with the program, type:

```

> harness.exe --help

```

The simplest execution is to load a module with an application loaded onto the processor(s) in the module:

The argument --modulefile <filename> states which shared object module¹ to simulate.

The argument --program <filename> states which program binary (elf) file to load to run on the processor(s)<sup>2</sup> contained within the module.

Look at some of the examples in Examples/PlatformConstruction.

<sup>1</sup> The module could also be loaded from a VLNV library using the --modulevendor, --modulelibrary, --modulename and --moduleversion arguments in place of the --modulefile argument.

<sup>2</sup> When no processor is specified the program elf file is loaded onto ALL the processors in the module. To specify programs to load onto a specific processor use --program modulename/processorname=app.elf

# 2.7 Writing a bespoke C test harness

If you require a more complex test harness, where you wish to control the simulator (for instance single step processor execution), or add monitors or other test related capabilities, then please refer to the Simulation Control of Platforms and Modules User Guide.

# 3 Describing a hardware design (a virtual platform)

There are three phases to describing a platform:

- 1. Creation of the design, which involves specifying the hardware components it contains along with the connections between those components.

- 2. Validation of the design, which involves ensuring that all the library elements which have been referenced are available in the library and that the connections are valid.

- 3. Use of that design with software programs designed to run on it in an appropriate test environment which allows the verification of both hardware and associated software. Each of these processes will be described in the sections that follow.

The first phase of the process of building a platform is to determine which hardware is to be included. A typical platform consists of a combination of modules, processors, buses, memory and other components.

The models for these are stored within the libraries. A library model does not need to exist within a library to be included in a platform, so a platform developer can work in parallel with a library model developer, however, the library elements must exist before verification of the design can take place. The exceptions to this are basic memories (RAM and ROM), FIFOs, packetnets, and buses for which models are provided with the tools.

The second phase is validating that the platform elaborates and connects up correctly - this is done simply by starting to simulate the platform but not executing instructions. This can be done by using the harness program, *harness.exe*, or it can be accomplished by using your own created harness / test bench written in C using the OP simulator control API.

The third phase is to use a test bench / harness to simulate the platform with appropriate application software and Operating Systems loaded.

# 3.1 Design hierarchy

With the use of the OP platform API, a platform can be constructed from a hierarchy of modules. A module is separately compiled and is a collection of component instances and connections. A module is like a sub-system. It can be used as a component in other modules or simulated directly by a harness. Connections can be made to modules using ports, and parameters can be passed in to configure some aspects of the module or its contained components, busses etc.

The term module instance is used to refer to the instantiation of a module in another module.

When connecting a bus, net, FIFO or packetnet to a module external port it is exported to the containing module that instances it. When not connected to a module external port it remains private within the created module.

| Modules can instance modules. |  |  |  |  |  |  |  |  |

|-------------------------------|--|--|--|--|--|--|--|--|

|                               |  |  |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |  |  |

|                               |  |  |  |  |  |  |  |  |

# 4 Creating and simulating a first virtual platform

Let us first walk through a simple example of using iGen to create a module of a simple CPU and memory, then use the provided harness.exe program to execute it with a cross compiled simple application program running on the CPU.

This platform has an OR1K CPU, RAM memory, bus and no hierarchy, as shown here:

# **Simple CPU and Memory**

Platform Memory Map

It is available in the directory:

\$IMPERAS\_HOME/Examples/PlatformConstruction/simpleCpuMemory

Take a copy of the example directory tree:

> cp -r \$IMPERAS\_HOME/Examples/PlatformConstruction/simpleCpuMemory .

## 4.1 A quick run through

First, we need to cross compile the application. If you do not have your own cross compiler tool chains, you can download pre-built tools for processors provided by OVP from the OVP website or Imperas user areas. For more information read the 'Installing Additional Tools' section of the Imperas Installation and Getting Started Guide.

Compile the application using the provided Makefile and specify the cross compile target to use:

```

> cd simpleCpuMemory/application

> make CROSS=OR1K

```

This uses Make to cross compile and link the application:

```

# Compiling application.c

# Linking application.OR1K.elf

```

Then make the module:

```

> cd ../module

> make

```

This uses Make to a) run iGen to take the input TCL file and create the output .c/.h files, and then b) host compile and link the platform.

If you do not have iGen installed, you will see the error message:

```

> make

# iGen Create OP MODULE module

make: igen.exe: Command not found

```

If you get that message, you need to download and install iGen (see section 2.2 above).

If iGen is installed, then you will see:

```

> make

# iGen Create OP MODULE module

# Copying STUBS module.c.igen.stubs to module.c

# Host Depending obj/Linux32/module.d

# Host Compiling Module obj/Linux32/module.igen.o

# Host Linking Module object model.so

```

Which will have created all the .c and .h files, and host compiled and linked them to shared object: model.so/.dll.

Now execute the simulation of the module with the compiled application using the provided harness.exe program:

The simulator will run; see that the 'Hello first world' is output...

```

OVPsim started: Tue Oct 13 10:57:22 2015

Hello first world from iGen generated platform

OVPsim finished: Tue Oct 13 10:57:22 2015

...

```

To make things simpler, we have provided a script that performs these make and run commands:

```

> ./example.sh

```

## 4.2 The simple application - Hello World

Look at the *application/application.c* file.

```

#include <stdio.h>

#include <stdlib.h>

int main(int argc, char **argv) {

printf("Hello first world from iGen generated platform\n");

return 0;

}

```

#### 4.2.1 How printf works using semihosting

For details on Imperas semihosting see the Imperas Installation and Getting Started User Guide.

In this example semihosting is used to provide behavior for the low level functions without having to add anything to the platform or application code. The *write* function invoked by the *printf* function called in the application is intercepted and the functionality provided by the simulator with, in this case, the printed characters that are written to stdout appearing in the simulator's output.

## 4.3 Defining the platform using iGen

The input to iGen is a tcl program/script that makes calls to the iGen platform/module building functions. iGen is run in a script or makefile to write out the .c/.h files that will be compiled to create and run the platform/module.

## 4.3.1 Creating a new module

Look at the *module/module.op.tcl* file.

```

ihwnew -name simpleCpuMemory

```

The command *ihwnew* starts the definition of a hardware component (module) and names it *simpleCpuMemory*.

# 4.3.2 Adding a bus

We then add a bus with name *mainBus* with the width of the address being 32 bits.

```

ihwaddbus -instancename mainBus -addresswidth 32

```

Note that you do not specify the data width of the bus, only the byte addressable range

#### 4.3.3 Adding a processor instance and connecting it up

A processor is added to the module with one function call:

This specifies an instance of the *generic* variant from the VLNV library of your Imperas installation *ovpworld.org/processor/or1k/1.0* using the semihost library of *or1kNewlib* and with an instance name of *cpu1*.

We connect it to the bus using:

```

ihwconnect -bus mainBus -instancename cpul -busmasterport INSTRUCTION ihwconnect -bus mainBus -instancename cpul -busmasterport DATA

```

This connects the *mainBus* to both master ports on the processor instance.

#### 4.3.4 Adding a memory and connecting it up

This instances a memory and connects up its port and provides the address range that it is usable at. Size is not specified as it is defined by the hi/lo byte addresses, i.e. its valid address range.

## 4.3.5 Full iGen listing for simple single core module

So in 7 lines of input for iGen we have created a simple module including a processor instance and a memory instance and connected them up.

# 4.3.6 Getting help on iGen module creating functions

To see a list of module building functions, visit the online documentation at:

```

IMPERAS_HOME/doc/api/igen/html/index.html

```

Or you could use the iGen --apropos command line argument to give information on a command:

```

> igen.exe --apropos ihwaddproc

NAME: ihwaddprocessor - Add to a design, an instance of a processor

ARGUMENTS:

-instancename <string> (mandatory)

The name for the new processor instance

-type <string>

The VLNV name of the processor

-variant <string>

The processor variant

-vendor <string>

The VLNV vendor name of the processor

-library <string>

The VLNV library name of the processor

-version <string>

The VLNV version number of the processor

-semihostname <string>

The VLNV name of a Semihost library

```

Note that for *ihwaddprocessor* there are many more arguments to set things like mips rate, start addresses, program image to load etc.

## 4.4 Running iGen

*igen.exe* is a program in the Imperas installation in the *IMPERAS\_HOME/bin/IMPERAS\_ARCH* directory and can be run from the command shell as illustrated above when using it to get help etc.

You can run *igen.exe* with the *--help* option to explore its command line options, but using igen.exe in a makefile or script for module generation is recommended and for our examples we will use the provided Makefile system.

The simplest way to run iGen is to use the Imperas provided Makefile system. In the examples we provide two files in the module directory, the *Makefile* and the *module.op.tcl* source file.

```

> cd module

> ls

Makefile module.op.tcl

```

The Imperas Makefile recognizes the file *module.op.tcl* as a script file to input to iGen to generate the module in C using the OP API.

```

> make

# iGen Create OP MODULE module

# Copying STUBS module.c.igen.stubs to module.c

# Host Depending obj/Linux32/module.d

# Host Compiling Module obj/Linux32/module.o

# Host Linking Module object model.so

```

#### 4.5 iGen generated module files

After iGen has been run you will find three files in the module directory; module.c, module.c.igen.stubs and module.igen.h.

The *module.c.igen.stubs* file is always generated and is overwritten each time iGen is run. The Make system will only invoke iGen if the input (module.op.tcl) file is newer than the generated files.

If module.c does not exist the stubs file, module.c.igen.stubs, is copied to create module.c.

If you look at the module.c and the module.igen.h files, you will see the OP API calls.

The file module.c can be edited and provides some empty callbacks in which you can add OP function calls to the module if you need to add more capability. Subsequent runs of iGen will write out a module.c.igen.stubs file that can be used for comparison and code merging purposes.

The *module.igen.h* file is always written and should not be modified by the user.

For details of the contents of the generated C files and the editing of them, see the Simulation\_Control\_of\_Platforms\_and\_Modules\_User\_Guide and Advanced\_Simulation\_Control\_of\_Platforms\_and\_Modules\_User\_Guide.

#### 4.6 Running the simulation using harness.exe

To run the simulation a harness or test bench is required. This can be written in C using OP API calls (see the Simulation Control of Platforms and Modules User Guide) or you can use the *harness.exe* program.

To use the *harness.exe* program to execute the simulation of the platform with the compiled application:

The simulator will run; see that the 'Hello first world' is output...

```

OVPsim started: Tue Oct 13 10:57:22 2015

Hello first world from iGen generated platform

OVPsim finished: Tue Oct 13 10:57:22 2015

```

To make things simpler, we have provided a script that performs these make and run commands:

```

> cd ..

> ./example.sh

```

You should be able to just edit the *application/application.c* and *module/module.op.tcl* files and then just run ./example.sh to rebuild, recompile, and run.

#### 4.6.1 The simulation command line

The Imperas simulators that are invoked by *harness.exe* and *iss.exe* have many common built-in command line arguments. Examples argument are *--modulefile* and *--program* as shown and used above, other useful arguments are *--trace*, *--verbose* as shown in the example below:

Use --help to see what each command line argument does.

Note that command line arguments like these can be added to the *example.sh* script invocation and they are passed to the simulator command line:

```

> ./example.sh --trace --verbose

> ./example.sh --help

```

# 5 Creating a module with a peripheral (a UART)

This example introduces peripherals. It builds on the module created in the previous example.

We expect you to look at the code in the example directory and in this text we will discuss those parts that are different or new when compared to the previous examples in this document.

This is an introductory example; please see later sections in this document for more detailed examples.

#### 5.1 Module overview

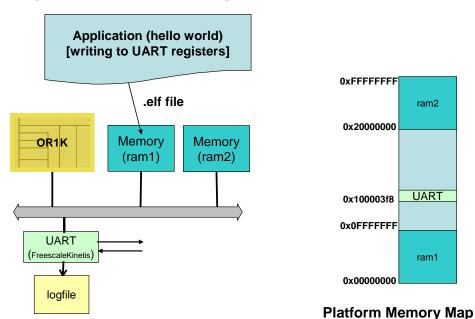

If you look at the picture below, you will see there is a CPU, two memories, and an instance of a UART in the platform.

# **Simple CPU Memory UART**

This platform is available at

\$IMPERAS\_HOME/Examples/PlatformConstruction/simpleCpuMemoryUart

Take a copy of the example directory tree:

> cp -r \$IMPERAS\_HOME/Examples/PlatformConstruction/simpleCpuMemoryUart .

#### 5.2 Quick run through

First we need to cross compile the application. If you do not have your own cross compiler tool chains, you can download pre-built tools for processors provided by OVP from the OVP website or Imperas user areas. For more information read the 'Installing Additional Tools' section of the Imperas Installation and Getting Started Guide.

Compile the application using the provided Makefile and specify the cross compile target to use:

```

> cd simpleCpuMemoryUart/application

> make CROSS=OR1K

```

This uses Make to cross compile and link the application:

```

# Compiling application.c

# Linking application.OR1K.elf

```

#### Then make the module:

```

> cd ../module

> make

```

This uses Make to a) run iGen to take the input tcl file and create the output .c/.h files, and then b) host compile and link the platform.

If you do not have iGen installed, you will see the error message:

```

> make

# iGen Create OP MODULE module

make: igen.exe: Command not found

```

If you get that message, you need to download and install iGen (see section 2.2).

If iGen is installed, then you will see:

```

> make

# iGen Create OP MODULE module

# Copying STUBS module.c.igen.stubs to module.c

# Host Depending obj/Linux32/module.d

# Host Compiling Module obj/Linux32/module.igen.o

# Host Linking Module object model.so

```

Which will have created all the needed .c and .h files, and host compiled and linked them to shared object model.so/.dll.

Now execute the simulation of the module with the compiled application using harness.exe:

The simulator will run; you will see the initialization of the UART and the writing to UART messages:

```

OVPsim started: Mon Nov 30 16:59:41 2015

Initializing KinetisUART

Writing to uart - see log file

OVPsim finished: Mon Nov 30 16:59:41 2015

```

The output of the UART is in the file uartTTY0.log:

```

> cat uartTTY0.log

Hello UARTO world

```

To make things simpler, we have provided a script that performs these make and run commands:

```

> ./example.sh

```

And don't forget you can use the verbose and other command line arguments, such as modeldiags:

```

> ./example.sh --modeldiags 0x3 --verbose

```

#### 5.3 The application - writing to the UART

Look at the *application/application.c* file.

Here is the declaration of a function to write a character to the UART:

The address of the UART is passed in as uartBase and this is used in ab\_S1 and ab\_D declared as volatile unsigned char so accesses to them will not be optimized away.

And then a *main* to call it:

```

#define UARTO_BASE ((unsigned char *) 0x100003f8)

int main(int argc, char **argv) {

initFreeScaleKinetisUart(UARTO_BASE);

```

Note the declaration of UARTO\_BASE to define the address where the UART is located in the platform.

Note also the call to initFreeScaleKinetisUart which is declared in *application.c* which just executes the initialization that you need to perform on the UART.

The application is compiled with:

```

> cd application

> make

# Compiling application.c

# Linking application.OR1K.elf

```

## 5.4 Defining the platform using iGen

The input to iGen is a tcl program/script that makes calls to the iGen platform/module building functions. iGen is run in a script or makefile to write out the .c/.h files that will be compiled to create and run the platform/module.

Look at the *module/module.op.tcl* file. Only new iGen commands will be introduced here. Please refer to the previous iGen example (in section 4.3.5) for description of the usage of iGen and information on starting a new module, adding a bus, processor, memories and connecting them up.

## 5.4.1 Adding nets to the module

To add nets to a module, use *ihwaddnet*:

```

ihwaddnet -instancename directWrite

ihwaddnet -instancename directRead

```

# 5.4.2 Adding a peripheral instance (a UART)

Adding a peripheral instance to a module is very similar to instancing a processor:

```

ihwaddperipheral -instancename periph0 \

-vendor freescale.ovpworld.org -library peripheral -version 1.0 \

-type KinetisUART

```

Note that when instancing a peripheral you must specify the vendor, library, and version.

OVP peripherals are documented on the OVP website. For this peripheral look at: OVPworld->Library->Peripherals->FreescalePeripherals->FreescaleKinetisUART.

#### 5.4.2.1 Setting a peripheral instance's parameters

Often a component you instance will have been declared with formal parameters or parameters that can be set when the component is instanced. (Check the documentation).

The FreescaleKinetisUART has many parameters that can be set including outfile. Parameters on an instance are set with ihwsetparameter:

```

ihwsetparameter -handle periph0 -name outfile -value uartTTY0.log -type string

```

This names the log file.

#### 5.4.2.2 Connecting up a peripheral instance to a bus and to nets

Check the documentation of the peripheral to see what you can connect to which ports.

The FreescaleKinetisUART has connections for a bus and nets:

This connects the peripheral's slave port to the bus and connects up the two netports to the nets.

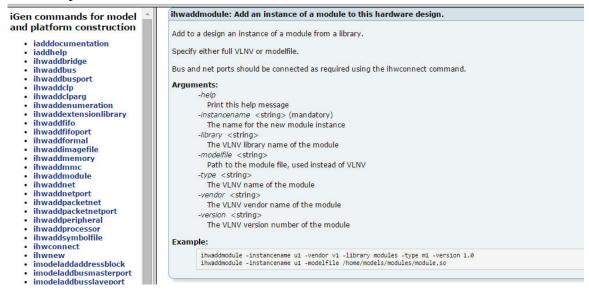

#### 5.4.3 Getting help on iGen module creating functions

To see a list of module building functions, visit the online documentation at:

```

IMPERAS_HOME/doc/api/igen/html/index.html

```

Or you could use the igen --apropos command line argument to give information on a command:

```

> igen.exe --apropos iseta

```

# 5.4.4 Full iGen listing for simpleCpuMemoryUart module

#### 5.5 Running iGen

*igen.exe* is a program in the Imperas installation in the \$IMPERAS\_HOME/bin/\$IMPERAS\_ARCH directory and can be run from the command shell as illustrated above when using it to get help etc.

You can run *igen.exe* with the *--help* option to explore its command line options, but using igen.exe in a makefile or script for module generation is recommended and for our examples we will use the provided Makefile system.

The simplest way to run iGen is to use the Imperas provided Makefile system. In the examples we provide two files in the module directory, the *Makefile* and the *module.op.tcl* source file.

```

> cd module

> ls

Makefile module.op.tcl

```

The Imperas make system recognizes the file *module.op.tcl* as a script file to input to iGen to generate the module in C using the OP API.

```

> make

# iGen Create OP MODULE module

# Copying STUBS module.c.igen.stubs to module.c

# Host Depending obj/Linux32/module.d

# Host Compiling Module obj/Linux32/module.o

# Host Linking Module object model.so

```

For additional information regarding the files generated by iGen for a module please refer to section 4.5 "iGen generated module files".

# 5.6 Running the simulation using harness.exe

To run the simulation a harness or test bench is required. This can be written in C using OP API calls (see the Simulation Control of Platforms and Modules User Guide), or you can use the provided *harness.exe* program.

To use the provided *harness.exe* program to execute the simulation of the platform with the compiled application:

The simulator will run, producing the following output:

```

OVPsim started: Tue Oct 13 10:57:22 2015

Initializing KinetisUART

Writing to uart - see log file

OVPsim finished: Tue Oct 13 10:57:22 2015

```

To make things simpler, we have provided a script that performs these make and run commands:

```

> ./example.sh

```

You should be able to edit the *application/application.c* and *module/module.op.tcl* files and then run ./example.sh to rebuild, recompile, and run.

#### 5.6.1 The simulation command line

The Imperas simulators, *harness.exe* and *iss.exe* have many common built-in command line arguments. Examples for *harness.exe* are *--modulefile* and *--program* as above, other useful arguments are:

Use --help to see what each command line argument does.

This lists many arguments (some of which will only be useful to specific simulators and models). The arguments are loosely grouped into categories - for example: control, debug, diagnostics, log, parameters, program and trace.

From the log group:

```

--verbose

```

which shows the simulation run statistics.

In the diagnostics group is:

```

--modeldiags 0x3

```

which shows the accesses to the peripheral models registers:

```

OVPsim started: Mon Nov 30 15:59:36 2015

Info (UART_UIS) top/periph0: Uart initialized in serial channel mode

```

```

Initializing KinetisUART

Info (UART_BRC) top/periph0: Baud rate changed to 19921

Info (UART_BRC) top/periph0: Baud rate changed to 19577

Info (UART_TFT) top/periph0: Transmitter fifo threshold set to 1

Info (UART_RFT) top/periph0: Receiver fifo threshold set to 1

Info (UART_UW) top/periph0: Write to Data register: data=0x0d ('')

Writing to uart - see log file

Info (UART_UW) top/periph0: Write to Data register: data=0x48 ('H')

Info (UART_UW) top/periph0: Write to Data register: data=0x65 ('e')

Info (UART_UW) top/periph0: Write to Data register: data=0x6c ('1')

Info (UART_UW) top/periph0: Write to Data register: data=0x6c ('1')

Info (UART_UW) top/periph0: Write to Data register: data=0x6f ('o')

Info (UART_UW) top/periph0: Write to Data register: data=0x20 (' ')

Info (UART_UW) top/periph0: Write to Data register: data=0x55 ('U')

Info (UART_UW) top/periph0: Write to Data register: data=0x41 ('A')

Info (UART_UW) top/periph0: Write to Data register: data=0x52 ('R')

Info (UART_UW) top/periph0: Write to Data register: data=0x54 ('T')

Info (UART_UW) top/periph0: Write to Data register: data=0x30 ('0')

Info (UART_UW) top/periph0: Write to Data register: data=0x20 (' ')

Info (UART_UW) top/periph0: Write to Data register: data=0x77 ('w')

Info (UART_UW) top/periph0: Write to Data register: data=0x6f ('o')

Info (UART_UW) top/periph0: Write to Data register: data=0x72 ('r')

Info (UART_UW) top/periph0: Write to Data register: data=0x6c ('l')

Info (UART_UW) top/periph0: Write to Data register: data=0x64 ('d')

Info (UART_UW) top/periph0: Write to Data register: data=0x0a ('')

Info (UART_UW) top/periph0: Write to Data register: data=0x0a ('')

OVPsim finished: Mon Nov 30 15:59:36 2015

```

#### Arguments:

```

--showbuses

--showdomains

```

show the connections to the buses and the memories.

From the trace group, examples are:

```

--trace

--trace --tracechange

```

These trace instructions in the processor with the option of tracing registers that have changed.

Note that command line arguments like the above can be added to the *example.sh* script invocation and they are passed to the simulator command line:

```

> ./example.sh --showbuses --showdomains

> ./example.sh --trace --tracechange

> ./example.sh --help

```

# 6 Changing the processor being used (From OR1K to ARM)

The example above as provided uses the OpenCores OR1K processor. It is easy to change this example to use another processor.

First check that the example runs unmodified.

```

> cp -r $IMPERAS_HOME/Examples/PlatformConstruction/simpleCpuMemoryUart .

> cd simpleCpuMemoryUart

> ./example.sh

> cd ..

```

Then copy the directories, and as we will be using an ARM processor name it accordingly:

```

> cp -r simpleCpuMemoryUart simpleCpuMemoryUart_ARM

> cd simpleCpuMemoryUart_ARM

```

In fact it takes 2 edits:

example.sh change the cross compilation target from:

```

CROSS=OR1K

```

to:

CROSS=ARM\_CORTEX\_A

*module/module.op.tcl* has changes to the selection of the processor model from:

```

ihwaddprocessor -instancename cpul \

-vendor ovpworld.org -library processor -type or1k -version 1.0 \

-semihostname or1kNewlib \

-variant generic

```

to:

```

ihwaddprocessor -instancename cpul \

-vendor arm.ovpworld.org -library processor -type arm -version 1.0 \

-semihostname armNewlib -semihostvendor arm.ovpworld.org \

-variant Cortex-A9UP

```

So thus we have changed the platform to use the *arm* model from *arm.ovpworld.org* as the variant *Cortex-A9UP* using semihost library *armNewlib* from vendor *arm.ovpworld.org* and changed the cross compiler make system to select the *ARM\_CORTEX\_A* tool chain.

Also note you will need to install the ARM toolchain (armv7.toolchain.<version>.<arch>.exe) (see installing tools chains above).

So running ./example.sh with our edits, will compile everything and run and we will see the UART log displayed at the end:

```

./example.sh --verbose

# Compiling application.c

# Linking application.ARM_CORTEX_A.elf

# Host Compiling Platform obj/Linux32/platform.o

# Host Linking Platform platform.Linux32.exe

# Host Linking Platform object model.so

OVPsim started: Mon Nov 30 16:11:47 2015

Info (OP_AL) Found attribute symbol 'modelAttrs' in file

ImperasLib/arm.ovpworld.org/processor/arm/1.0/model.dll'

Info (OP_AL) Found attribute symbol 'modelAttrs' in file

ImperasLib/arm.ovpworld.org/semihosting/armNewlib/1.0/model.dll'

Info (OR_OF) Target 'simpleCpuMemoryUart/cpul' has object file read from

'application/application.ARM_CORTEX_A.elf'

Info (OR_PH) Program Headers:

Info (OR_PH) Type Offset

VirtAddr

PhysAddr

FileSiz

Flags Align

Info (OR_PD) PROC 0x0000a34c 0x0000a34c 0x00000008 0x00000008

R-- 4

R-E 8000

Info (OR_PD) LOAD 0x0000a358 0x00012358 0x00012358 0x00000854 0x00100ca8

RW-

8000

Initializing KinetisUART

Writing to uart - see log file

Info -----

Info PSE SIMULATION TIME STATISTICS

Info 0.00 seconds: PSE THREAD 'simpleCpuMemoryUart/periph0'

Info 0.01 seconds: PSE 'simpleCpuMemoryUart/periph0' (and 90 terminated

callbacks)

Info -----

Info

Info ------

Info CPU 'simpleCpuMemoryUart/cpu1' STATISTICS

Info Final program counter : 0x8030

Info Simulated instructions: 2,492

Info Simulated MIPS : run too short for meaningful result

Info -----

Info

Info -----

Info SIMULATION TIME STATISTICS

Info Simulated time : 0.00 seconds

Info User time

: 0.04 seconds

Info ------

OVPsim finished: Mon Nov 30 16:11:47 2015

Hello UARTO world

```

# 7 Adding Bus Bridges, Aliasing address regions

A bus bridge is a generic component (it does not exist in a library) which maps part or all of the address space of one bus to the address space of another.

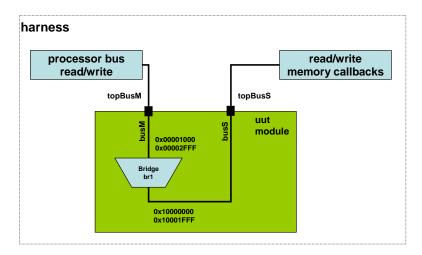

#### 7.1 Static Bus bridges

Construction of the processor, memory and peripheral components has already been covered.

A static bridge may be used to map sections of one address space to another. It is also used to create aliases of memory.

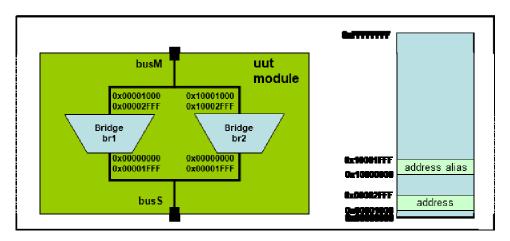

In this example a processor read/write in the address range 0x00001000 to 0x00002fff will be mapped to a memory access in the range 0x10000000 to 0x10001fff.

This example is available at

\$IMPERAS\_HOME/Examples/PlatformConstruction/busHierarchy

Take a copy of the example directory tree:

```

> cp -r $IMPERAS_HOME/Examples/PlatformConstruction/busHierarchy .

> cd busHierarchy

```

There are three parts to a bridge.

The instance definition:

```

ihwaddbridge -instancename br1

```

The slave port connection onto the bus containing the bus master:

```

ihwconnect -bus busM -busslaveport ps -instancename br1 \

-loaddress 0x1000 -hiaddress 0x00002fff

```

The master port connection onto the bus containing the bus slaves:

Note that in this example *busM* refers to the bus on which the bus master accesses are carried out and onto which the bridge slave port is connected and *busS* is the bus which is connected to the slaves and onto which the bridge master port is connected. The port names are for documentation only but should be unique on their respective busses.

The definition above is executed by iGen to generate a C definition in which the function *opBridgeNew* creates the bus bridge:

Note that the port is identified as a slave port by the setting of slave=1.

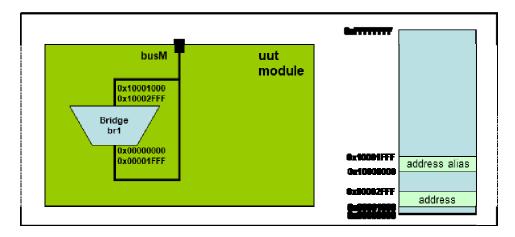

#### 7.1.1 Aliasing

A bus bridge can be used to alias a region of an address space to another region on the same bus. There are two ways this could be achieved:

#### 7.1.1.1 Using a single bus bridge to map a region back onto the same bus

```

ihwaddbridge -instancename br1

ihwconnect -bus busM -busslaveport ps -instancename br1 \

```

```

-loaddress 0x10000000 -hiaddress 0x10002fff

ihwconnect -bus busM -busmasterport pm -instancename br1 \

-loaddress 0x00000000 -hiaddress 0x00001fff

```

This is valid in OVP but if trying to generate a SystemC TLM platform it is not possible to map regions back onto the same bus.

#### 7.1.1.2 Using a separate bus and two bridges to map a region

An alternate method, and recommended as this overcomes a failure in SystemC, is to create a second bus on which the components and memory are located separately to the bus masters which see the aliased memory. This requires the use of two bus bridges, one to make the original mapping and the second to make the aliased mapping.

#### 7.1.1.3 Using bridges to model unconnected top address bit

This example models the effect of not connecting the most significant address bit of a 32-bit bus: addresses in the top half of the address space are mapped to the bottom half.

From which iGen generates the following C function usage

#### 7.2 Dynamic Bus Bridges

#### 7.2.1 Introduction

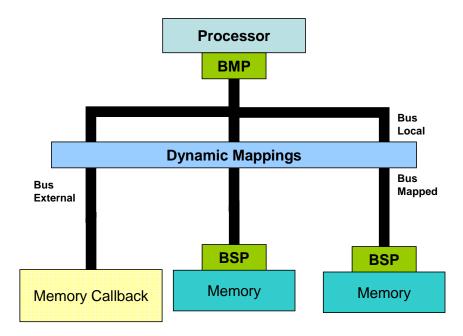

A dynamic bus bridge allows a testbench or module to make dynamic changes to the address space visible on a bus. It can map part or all of the address space of one bus to the address space of another.

A dynamic bus bridge creates a mapping between two busses that, essentially, makes the region on the slave bus appear directly connected onto the master bus at the address range specified.

Any previously bridged addresses within a new mapped region are removed. However, the underlying memory of a mapping is not affected so that a subsequent mapping back onto an address region will make the same memory visible once again.

This diagram illustrates the example in

$\verb|SIMPERAS_HOME/Examples/SimulationControl/dynamicBridge|\\$

The bridge, as part of the module definition, is initially used to map the full extent of the processor address map of the 'local' bus to the 'mapped' bus. As the program executes

the testbench dynamically re-maps the busses so that an address region accessed by the program is

- 1. mapped from the 'mapped' bus to the 'external' bus

- 2. mapped back from the 'external' bus to the 'mapped' bus, allowing previous values to be accessed.

- 3. unmapped, so that an access to the region will create a memory fault.

The module contains a single processor and memory and is defined in

```

$IMPERAS_HOME/Examples/SimulationControl/dynamicBridge/platform/cpuSystem/module

.op.tcl

```

The processor and the memory are connected onto separate busses with an initial bus bridge mapping the full address extent from the local processor connected bus to the bus on which the memory is connected. This is created as part of the module using:

The testbench is used to instantiate the module and then perform the re-mapping of the connections between the local and mapped busses as the application program is executed on the processor.

The 'subSystem' module is instantiated as 'u1'.

In order to modify the mappings from the testbench the objects must be discovered from the module.

```

busLocal = opObjectByName(mi, "u1/busLocal", OP_BUS_EN ).Bus;

busMapped = opObjectByName(mi, "u1/busMapped", OP_BUS_EN ).Bus;

```

These objects may then be used to dynamically change the mappings between the busses.

Mappings may be made to connect the local bus to an alternate external test bus

or to map back to the original bus

```

opDynamicBridge(object->busLocal,object->busMapped,

0x00400000, 0x0040000f,0x00400000);

```

and if required a mapping can be deleted, leaving a 'hole' in the memory address.

#### 7.2.2 Running the simulation

The testbench harness is compiled to an executable for simulation execution. The standard command line parser is included to allow ease of use.

To build the testbench, modules and a simple test application Makefiles are used.

For compilation of the application take a copy and build it:

```

> cp -r $IMPERAS_HOME/Examples/SimulationControl/dynamicBridge .

> cd dynamicBridge

> make -C application

```

And to use iGen to generate the platform and then to build

```

> make -C module

> make -C harness

```

The execution of the testbench is performed with the call to the compiled executable:

So that we can see what is happening in this testbench execution optional arguments are added to the command line to turn on tracing of instruction execution --trace and also register change --tracechange.

When the example script is executed the following should be observed:

The building of the testbench and module components:

```

make: Entering directory 'application'

Compiling Application asmtest.OR1K.o

Linking Application asmtest.OR1K.elf

make: Leaving directory 'application'

make: Entering directory 'module'

# iGen Create OP MODULE module

# Copying STUBS module.c.igen.stubs to module.c

# Host Depending obj/Linux32/module.d

make: Leaving directory 'module'

make: Entering directory 'module'

# Host Compiling Module obj/Linux32/module.o

# Host Linking Module object model.so

make: Leaving directory 'module'

```

```

make: Entering directory 'harness'

# Host Depending obj/Linux32/harness.d

make: Leaving directory 'harness'

make: Entering directory 'harness'

# Host Compiling Platform obj/Linux32/harness.o

# Host Linking Platform harness.Linux32.exe

# Host Linking Platform object model.so

make: Leaving directory 'harness'

```

The execution of the testbench with application on the processor.

Testbench initialization and setup:

```

Info (harness) Setting up bus regions as callbacks on test bus (busExternal)

Info (harness) Root Module Simulate Phase

Info (harness) Find processor 'ul/cpul'

Info (harness) Processor 'ul/cpul': Run for 10 instructions

```

The execution of a fixed number of instructions of the test application on the processor, instruction and register change tracing. This shows the write of 0x1234 to address 0x00400000 and the subsequent read back of the same value from that address with the default mapping in place:

```

Info R2 deadbeef -> 00000001

Info 'u1/cpu1', 0x000000000100007c(_start+8): 1.addi r3,r0,0x1234

Info R3 deadbeef -> 00001234

Info R4 deadbeef -> 00000800

Info 'u1/cpu1', 0x0000000001000084(_start+10): 1.muli

r4,r4,0x800

R4 00000800 -> 00400000

Info 'u1/cpu1', 0x000000001000088(_start+14): 1.sw

0x0(r4),r3

Info 'u1/cpu1', 0x000000000100008c(_start+18): 1.nop

0x0

Info 'u1/cpu1', 0x000000001000090(_start+1c): 1.1wz

r5,0x0(r4)

Info R5 deadbeef -> 00001234

Info 'u1/cpu1', 0x000000001000094(_start+20): 1.nop

0x0

Info 'u1/cpu1', 0x000000001000098(_start+24): 1.nop

0x0

Info (harness) Processor 'ul/cpul' stopped for reason 'Scheduler has expired'

```

The previous instructions were completed and the testbench modifies the mapping of a region from 0x00400000 to 0x004000ff so that it now maps to a bus created in the testbench and that includes callbacks to monitor any access.

The execution of the next fixed number of instructions of the test application on the processor shows the read from address 0x00400000 trigger the testbench read callback which returns the value 0x00000000.

```

Info (harness) Processor 'ul/cpul' stopped for reason 'Scheduler has expired'

Info (harness) Bridge region of 'busLocal' to 'busExternal'

Info (harness) Processor 'u1/cpu1': Run for 4 instructions

Info 'ul/cpul', 0x000000000100009c(_start+28): 1.nop

Info 'u1/cpu1', 0x00000000010000a0(_start+2c): 1.lwz

r5,0x0(r4)

Info (harness_RCB) readCallback: busExternal, 0x400000

Info R5 00001234 -> 00000000

Info 'u1/cpu1', 0x0000000010000a4(_start+30): 1.nop

```

```

Info 'u1/cpu1', 0x0000000010000a8(_start+34): l.nop 0x0

Info (harness) Processor 'u1/cpu1' stopped for reason 'Scheduler has expired'

```

The previous instructions were completed and the testbench modifies the mapping of a region from 0x00400000 to 0x0040000f so that it now maps back to the original bus and hence the original memory content.

The execution of the next fixed number of instructions of the test application on the processor shows the read from address 0x00400000 returns the value 0x00001234.

The previous instructions were completed and the testbench modifies the mapping of a region from 0x00400000 to 0x0040000ff to remove all mappings.

The execution of the next fixed number of instructions of the test application on the processor shows the read from address 0x00400000 causes a read exception i.e. the memory access fails.

# 8 Byte Swapping (Endian Correction)

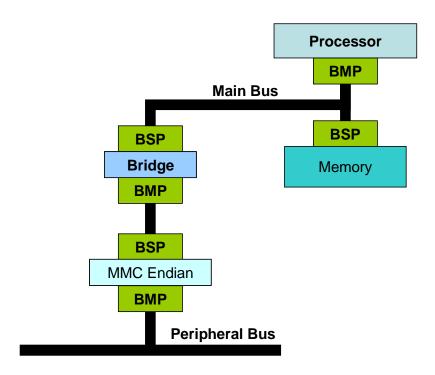

A bus controller in a real platform might have the ability to perform byte-swapping on each bus cycle. This allows, for example, a big-endian processor to communicate with a little-endian peripheral component. CpuManager supports byte swapping through the use of an MMC. The bus is broken into two and an MMC inserted between the two parts.

#### 8.1 Bus Connections

An MMC creates a one-way connection between two busses, accepting bus cycles from one bus and passing them to another. An MMC cannot perform address decoding so is activated by accesses to all addresses. If the swapping function is required for a limited address range, a bus bridge is used to decode the required range, and its output passed to the MMC.

This example is listed in:

\$IMPERAS\_HOME/Examples/PlatformConstruction/byteSwapperMMC

The OR1K processor uses two RAMs (one shown) for program and stack. The bridge maps a limited address range from the main bus onto an intermediate bus which is connected to the MMC model *endianSwap* which can be found in the ovpworld.org mmc library. A simple peripheral model (not shown) is connected to the peripheral bus.

Thus, the processor has direct access to its memory without byte-swapping, but a 32-bit access (read or write) to the peripheral will have its bytes reversed.

Note that in this design, a bus master on the peripheral bus will be unable to access the processor memory.

Look at the module definition in the example in:

```

$IMPERAS_HOME/Examples/PlatformConstruction/byteSwapperMMC/module/module.op.tcl

```

This shows the instantiation of the components as shown in the above diagram. This includes the instantiation of the byteSwap MMC model from the VLNV library.

```

ihwaddmmc -instancename swap \

-vendor "ovpworld.org" -library "mmc" -type "endianSwap" -version "1.0"

```

Which is connected between the two busses, *busInter* (which maps to a small address space in the processor memory space) and *busPeripheral* (which includes the peripheral).

```

ihwconnect -bus busInter -instancename swap -busslaveport spl

ihwconnect -bus busPeripheral -instancename swap -busmasterport mpl

```

The module is executed using the Imperas harness by passing the module shared object (dynamic link library) and the program to be loaded (note: run example.sh to compile the application and module first):

```

harness.exe --modulefile module/model.so \

--program application/application.OR1K.elf

```

The peripheral model is a simple programmer's interface model. This provides registers that can be accessed, in this case all are read only, which are initialized at reset to known values.

When executed the following should be observed

```

./example.sh

Starting

R0 = 0x01020304

R1 = 0x11121314

R2 = 0x21222324

R3 = 0x31323334

Done

Info (endianSwap) TOTAL SWAPPED BYTES: 16

```

The four registers of the peripheral have been accessed and a byte swapped version of the data displayed.

#### 8.2 Performance considerations

In the simulator, the byte swapping MMC converts a memory access to a function call, hence a byte-swapper model should be used with care; a byte-swapper placed between a processor and its main memory (program or data) will severely restrict its performance. However, putting a byte-swapper between a processor and a peripheral model will cause

| minimal effect because the peripheral behavior is itself modeled by function calls and here will be comparatively few accesses to the peripheral device. |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                          |  |

|                                                                                                                                                          |  |

|                                                                                                                                                          |  |

|                                                                                                                                                          |  |

|                                                                                                                                                          |  |

|                                                                                                                                                          |  |

|                                                                                                                                                          |  |

|                                                                                                                                                          |  |

|                                                                                                                                                          |  |

|                                                                                                                                                          |  |

|                                                                                                                                                          |  |

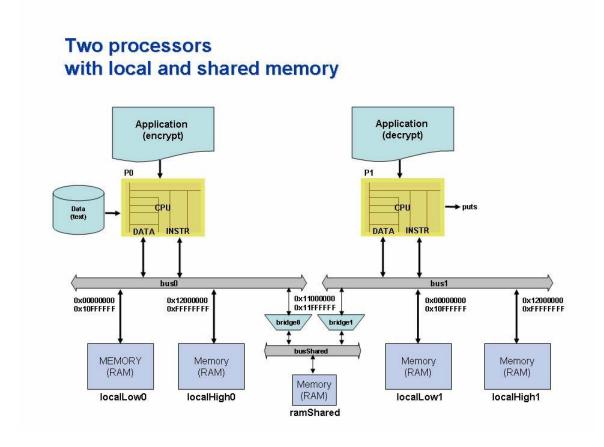

# 9 Two processors with shared memory

The following diagram shows the example hardware design to be built. It is a two-processor design with both local and shared memory.

This example is documented in:

\$IMPERAS\_HOME/Examples/PlatformConstruction/twoProcessorSharedMemory

## 9.1 Adding Hardware Elements

The first step is to add the hardware elements.

Each element is added in turn. This design contains 2 processors, 5 ram elements, 2 bridge elements and the associated interconnect. These elements are in the standard library; however, no checking takes place at this stage to ensure that the library models exist. This means that it is possible to create the hardware design before the models are completed.

Components can be added in any order, though this design starts with the processors. This requires a choice of processor type – in this case an or1k – and a unique instance name by which it can be identified. The command used is *ihwaddprocessor*

This command has other options not listed here. You can use the command:

```

> igen.exe --apropos addprocessor

```

for more information. The meanings of simulation options are documented in the simulator manual. Example:

```

# add the processors

ihwaddprocessor -type orlk -instancename P0 -semihostname orlkNewlib -variant

generic

ihwaddprocessor -type orlk -instancename P1 -semihostname orlkNewlib -variant

generic

```

This adds two OR1K processors to the design with unique instance names P0 & P1. In this case the name of a semi-host library has been specified but this is optional.

RAM is added using the *ihwaddmemory* command as follows. This refers to the simple built-in model. There are two kinds of memory that can be added in this way; *ram* which can be read or written and *rom* which can be loaded from an imagefile, but not written by other hardware. The *ram* and *rom* components are generic so can be connected with any address range - their size adjusts accordingly and is specified by the *ihwconnect* command. Specifically, sized memories can be added to your library if it is required to restrict the design to use 'real' components.

```

# add memories (local and shared)

ihwaddmemory -type ram -instancename localLow0

ihwaddmemory -type ram -instancename localHigh0

ihwaddmemory -type ram -instancename localLow1

ihwaddmemory -type ram -instancename localHigh1

ihwaddmemory -type ram -instancename ramShared

```

Buses and Bridges are added using the *ihwaddbus* and *ihwaddbridge* commands as follows

```

# add the buses

ihwaddbus -instancename bus1     -addresswidth "32"

ihwaddbus -instancename bus0     -addresswidth "32"

ihwaddbus -instancename busShare -addresswidth "32"

# add the bus bridges

ihwaddbridge -instancename bridge0

ihwaddbridge -instancename bridge1

```

This adds three buses and two bridge elements. Again, all have unique names and, in the case of the buses, the address width has been specified.

## 9.2 Making Connections

Component instances need to be connected using the *ihwconnect* command. This allows the user to specify the precise details of how the elements are connected together. There are a number of different kinds of connection; some are a simple connection of one element to another, others are more complex and require the specification of address ranges.

*ihwconnect* is used to make all connections. In the design example shown above, the connections need to be made between each processor and its associated bus, between each bus and the memory elements and between the bus and the bridge elements.

Connections are made by reference to either the unique instance names which were specified in the ihwadd\* commands, and the name of the port being connected, or to an external port on this design.

bus0 and bus1 have connections to:

- Master port connection to the DATA and INSTRUCTION ports of the processor

- Slave port connections to the low and high local memories

- A slave port connection to a bridge to the shared memory

busShare has connections to:

- Master port connections to each of the bus bridges

- A slave port connection to the shared memory

These connections are added as shown here:

```

# add the processor connections

ihwconnect -bus bus0 -instancename P0 -busmasterport "INSTRUCTION" ihwconnect -bus bus0 -instancename P0 -busmasterport "DATA" ihwconnect -bus bus0 -instancename localLow0 -busslaveport "sp0" \

-loaddress "0x00000000" -hiaddress "0x10ffffff"

ihwconnect -bus bus0 -instancename bridge0 -busslaveport "sp0" \

-loaddress "0x11000000" -hiaddress "0x11ffffff"

ihwconnect -bus bus0 -instancename localHigh0 -busslaveport "sp0" \

-loaddress "0x12000000" -hiaddress "0xffffffff"

# add connections to bus1

ihwconnect -bus busl -instancename Pl -busmasterport "INSTRUCTION" ihwconnect -bus busl -instancename Pl -busmasterport "DATA"

ihwconnect -bus bus1 -instancename localLow1 -busslaveport "sp1" \

-loaddress "0x00000000" -hiaddress "0x10ffffff"

ihwconnect -bus busl -instancename bridgel -busslaveport "spl" \

-loaddress "0x11000000" -hiaddress "0x11fffffff"

ihwconnect -bus busl -instancename localHighl -busslaveport "sp1"

-loaddress "0x12000000" -hiaddress "0xffffffff"

# add connections to busShare

ihwconnect -bus busShare -instancename bridge0 -busmasterport "mp0" \

-loaddress "0x00000000" -hiaddress "0x00fffffff"

ihwconnect -bus busShare -instancename bridgel -busmasterport "mp1"" \

-loaddress "0x00000000" -hiaddress "0x00fffffff"

ihwconnect -bus busShare -instancename ramShared -busslaveport "sp0"" \

-loaddress "0x00000000" -hiaddress "0x00fffffff"

```

Slave port connections must always have an address range specifying the input addresses that will map to that port.

A bridge supports uni-directional transfers from the slave port to the master port i.e. a master on one bus accesses the slave port and this is translated to an access from the master port onto a second bus. This requires the specification of address ranges using the *—loaddress* and *—hiaddress* options for both the master and slave ports.

## 9.3 The example encrypt and decrypt applications

An example application is provided in the applications directories, one for each processor. The applications illustrate that accesses are being performed in the shared memory region. Each processor has its own private memory to hold the program and the stack and data sections.

The first application, encrypt, reads input from a text file, does a trivial byte by byte encryption by xor'ing each byte read with the next value returned by rand(), and places each encrypted byte into a frame buffer. When the frame buffer is full (or the end of the file is reached) the value of ENCRYPT\_INDEX, which is in shared memory, is incremented.

The source of the encrypt application is:

```

#include <stdio.h>

#include <stdlib.h>

#include "sharedData.h"

// Main routine

int main(int argc, char **argv) {

bufferP buffer = SHARED_BLOCK;

const char *fileName = argc < 2 ? "constitution.txt" : argv[1];</pre>

FILE *file = fopen(fileName, "r");

int findex = 0;

int finds

int done

size_t num;

done = 0;

// seed random number generator

srand(RAND_SEED);

// check file can be opened

if(!file) {

printf("Unable to open file %s for read\n", fileName);

return -1;

}

// handle each frame of data

while(!done && (findex<NUM_FRAMES)) {</pre>

```

```

// read next frame of data from input file

num = fread(&buffer->frame[findex], 1, FRAME_SIZE, file);

// identify the last frame being sent

// note: this assumes input data does not include a 0 (e.g. text file)

if(num!=FRAME_SIZE) {

buffer->frame[findex][num] = 0;

done = 1;

}

// encrypt each character in the frame

for(i=0; i<FRAME_SIZE; i++) {

buffer->frame[findex][i] ^= rand();

}

// step to the next frame

*ENCRYPT_INDEX = ++findex;

}

return 0;

}

```

The decrypt application watches for the ENCRYPT\_INDEX value in shared memory to be incremented by the encrypt application. When it has been incremented it decrypts each byte in the next frame into a local buffer and then writes the buffer to stdout (which is semihosted to the simulator console).

The source of the decrypt application is:

```

#include <stdio.h>

#include <stdlib.h>

#include "sharedData.h"

#define TIMEOUT 100000

// Wait until the next frame is ready

void waitForFrame(int findex) {

int idleCount = 0;

while(findex == *ENCRYPT_INDEX) {

if (idleCount++ >= TIMEOUT) {

printf ("Timeout waiting for frame %d\n", findex);

exit(-1);

}

}

// Main routine

int main(int argc, char **argv) {

bufferP buffer = SHARED_BLOCK;

int findex = 0;

int ch = -1;

```

```

char

writeBuf[FRAME_SIZE+1];

// seed random number generator

srand(RAND_SEED);

// write each decrypted frame as it is ready until entire message is sent

while(ch && (findex<NUM_FRAMES)) {</pre>

int i;

// spin until encrypted frame is prepared

waitForFrame(findex);

// decrypt each character in the frame

for(i=0; (i<FRAME_SIZE) && ch; i++) {</pre>

ch = writeBuf[i] = (buffer->frame[findex][i] ^ rand());

// terminate the string to write

writeBuf[i] = 0;

// write output

printf("\n**** FRAME %i ****\n\n", findex);

puts(writeBuf);

fflush(0);

// step to next frame

findex++;

return 0;

```

The files *shared.h* and *sharedData.h* define values that are used in both the encrypt and decrypt applications:

*shared.h* defines the location of the shared memory:

```

// these define the shared memory range